# TOSHIBA

### CMOS 32-Bit Microcontroller TMP94C251AF

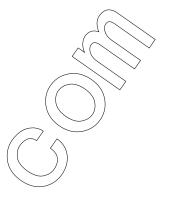

### 1. Outline and Device Characteristics

TMP94C251A is high-speed advanced 32-bit microcontroller developed for controlling equipment which processes mass data.

TMP94C251A is a microcontroller which has a high-performance CPU (900/H2 CPU) and various built-in I/Os. And TMP94C251A is enhanced memory interface functions TMP94C251AF is housed in an 144-pin mini flat package.

Device characteristics are as follows:

- (1) CPU: 32-bit CPU (900/H2 CPU)

- Compatible with TLCS-900, 900/L, 900/L1, 900/H's instruction code

- 16 Mbytes of linear address space

- General-purpose registers and register banks

- Micro DMA: 8 channels (250 ns/4 bytes at 20 MHz) .

- (2) Minimum instruction execution time: 50 ns (at 20 MHz)

- (3) Internal memory

- Internal RAM: 2 Kbytes (can use for code section)

- Internal ROM: None

- (4) External memory expansion

- Expandable up to 16 Mbytes (shared program/data area)

- Can simultaneously support 8-/16-bit width external data bus

- (5) Memory controller

- Chip select output: 6 channels

- (6) DRAM Controller: 2 channels

- Direct interface (supported 8-/16-bit external data bus)

030619EBP1

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.. The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunctionor failure of Unich cause less of human life or bodily injury ("Unitended Usage"). Unitended Usage include adout serve control failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy contro instruments, aliphane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk

The products described in this document are subject to the foreign exchange and foreign trade laws. TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

- (7) 8-bit timer: 4 channels

- (8) 16-bit timer: 4 channels

- (9) Serial interface: 2 channels

- (10) 10-bit AD converter: 8 channels (with sample hold circuit)

- (11) 8-bit DA converter: 2 channels (with CMOS-AMP)

- (12) Watchdog timer

- (13) Interrupt controller

- 18 internal interrupts

- 10 external interrupts

- (14) I/O port: 64 pins

- (15) Package: 144-pin QFP (P-QFP144-2020-0.50)

Figure 1.1 TMP94C251A Block Diagram

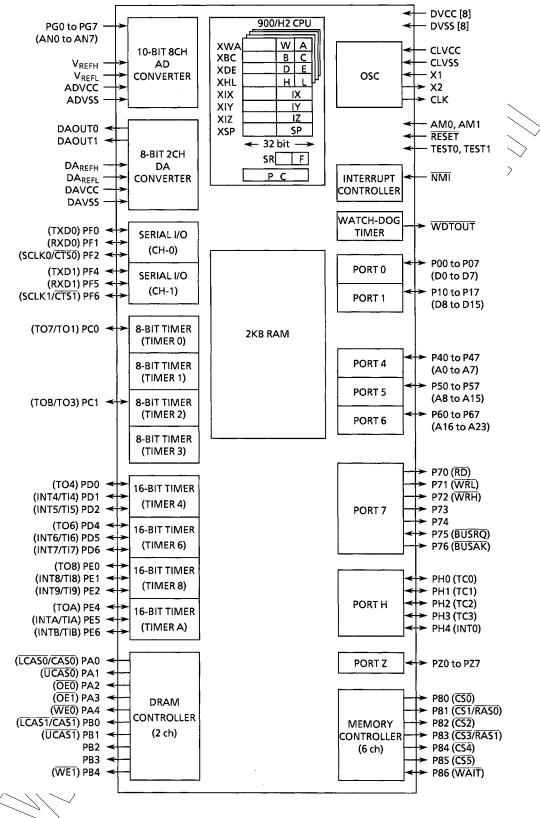

## 2. Pin Assignment and Functions

### 2.1 Pin Assignment (Top view)

### 2.2 Pin Names and Functions

The names of input/output pins and their functions are described below.

| Pin Name               | Number<br>of Pins | I/O        | Functions                                                                                                                                                                          |  |  |

|------------------------|-------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| P00 to P07<br>D0 to D7 | 8<br>(TTL)        | I/O<br>I/O | Port 0: I/O port Data: 0 to 7 for data bus                                                                                                                                         |  |  |

|                        | (112)             | 1/0        | TMP94C251A is external ROM type, these pins are initialized to this function.<br>When TMP94C251A doesn't access external memories, these pins are put in the high-impedance state. |  |  |

| P10 to P17             | 8                 | I/O        | Port 1: I/O port                                                                                                                                                                   |  |  |

| D8 to D15              | (TTL)             | I/O        | Data: 8 to15 for data bus                                                                                                                                                          |  |  |

|                        |                   |            | If TMP94C251A is external ROM type and is start with 16 bit data bus, these pins are initialized to this function.                                                                 |  |  |

|                        |                   |            | When TMP94C251A doesn't access external memories, these pins are put in the high-impedance state.                                                                                  |  |  |

| P40 to P47             | 8                 | I/O        | Port 4: I/O port                                                                                                                                                                   |  |  |

| A0 to A7               |                   | Output     | Address: 0 to 7 for address bus                                                                                                                                                    |  |  |

|                        |                   |            | TMP94C251A is external ROM type, these pins are initialized to this function.                                                                                                      |  |  |

|                        |                   |            | When TMP94C251A doesn't access external memories, these pins don't change.                                                                                                         |  |  |

| P50 to P57             | 8                 | I/O        | Port 5: I/O port<br>Address: 8 to 15 for address bus                                                                                                                               |  |  |

| A8 to A15              |                   | Output     | TMP94C251A is external ROM type, these pins are initialized to this function.                                                                                                      |  |  |

|                        |                   |            | When TMP94C251A doesn't access external memories, these pins don't change.                                                                                                         |  |  |

| P60 to P67             | 8                 | I/O        | Port 6: I/O port                                                                                                                                                                   |  |  |

| A16 to A23             | Ŭ                 | Output     | Address: 16 to 23 for address bus                                                                                                                                                  |  |  |

|                        |                   |            | TMP94C251A is external ROM type, these pins are initialized to this function.                                                                                                      |  |  |

|                        |                   |            | When TMP94C251A doesn't access external memories, these pins don't change.                                                                                                         |  |  |

| P70                    | 1                 | Output     | Port 70: Output port (output "high" when initialized)                                                                                                                              |  |  |

| RD                     |                   | Output     | Read: Strobe signal for reading external memory                                                                                                                                    |  |  |

|                        |                   |            | When TMP94C251A doesn't access external memory, doesn't output strobe.                                                                                                             |  |  |

|                        |                   |            | TMP94C251A is external ROM type, these pins are initialized to this function.                                                                                                      |  |  |

| P71                    | 1                 | Output     | Port 71: Output port (output "high" when initialized)                                                                                                                              |  |  |

| WRL                    |                   | Output     | Write LL: Strobe signal for writing data on pins D0 to D7                                                                                                                          |  |  |

|                        |                   |            | When TMP94C251A doesn't access external memory, doesn't output strobe.                                                                                                             |  |  |

| P72                    | 1                 | Output     | Port 72: Output port (output "high" when initialized)                                                                                                                              |  |  |

| WRH                    |                   | Output     | Write LH: Strobe signal for writing data on pins D8 to D15                                                                                                                         |  |  |

|                        | ļ                 |            | When TMP94C251A doesn't access external memory, doesn't output strobe.                                                                                                             |  |  |

| P73                    | 1                 | Output     | Port 73: Output port (output "high" when initialized)                                                                                                                              |  |  |

| P74                    | 1                 | Output     | Port 74: Output port (output "high" when initialized)                                                                                                                              |  |  |

| Table 2.2.1 | Pin Names and Functions (1/6)        |

|-------------|--------------------------------------|

| 10016 2.2.1 | 1 in Marines and 1 uncliding $(1/0)$ |

| Pin Name | Number<br>of Pins | I/O    | Functions                                                                                         |  |

|----------|-------------------|--------|---------------------------------------------------------------------------------------------------|--|

| P75      | 1                 | I/O    | Port 75: I/O port                                                                                 |  |

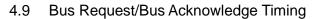

| BUSRQ    |                   | Input  | Bus request: Signal used to request high impedance for memory interface signals. If these         |  |

|          |                   |        | signals are used as port, there are not change. The memory interface signals are follows:         |  |

|          |                   |        | A0 to A23, D0 to D15, RD, WRLL, WRLH                                                              |  |

|          |                   |        | The output signals of memory controller.                                                          |  |

| P76      | 1                 | Output | Port 76: Output port (output "high" when initialized)                                             |  |

| BUSAK    |                   | Output | Bus acknowledge: Signal indicating that request of $\overline{	extsf{BUSRQ}}$ signal is accepted. |  |

| P80      | 1                 | Output | Port 80: Output port (output "high" when initialized)                                             |  |

| CS0      |                   | Output | Chip select 0: Outputs "low" if address is within specified address area.                         |  |

| P81      | 1                 | Output | Port 81: Output port (output "high" when initialized)                                             |  |

| CS1      |                   | Output | Chip select 1: Outputs "low" if address is within specified address area.                         |  |

| RAS0     |                   | Output | Row address strobe 0: Outputs RAS strobe for DRAM if address is within specified address area.    |  |

| P82      | 1                 | Output | Port 82: Output port (output "high" when initialized)                                             |  |

| CS2      |                   | Output | Chip select 2: Outputs "low" if address is within specified address area.                         |  |

| P83      | 1                 | Output | Port 83: Output port (output "high" when initialized)                                             |  |

| CS3      |                   | Output | Chip select 3: Outputs "low" if address is within specified address area.                         |  |

| RAS1     |                   | Output | Row address strobe 1: Outputs RAS strobe for DRAM it address is within specified address area.    |  |

| P84      | 1                 | Output | Port 84: Output port (output "high" when /initialized)                                            |  |

| CS4      |                   | Output | Chip select 4: Outputs "low" if address is within specified address area.                         |  |

| P85      | 1                 | Output | Port 85: Output port (output "high when initialized)                                              |  |

| CS5      |                   | Output | Chip select 5: Outputs "low" if address is within specified address area.                         |  |

| P86      | 1                 | I/O    | Port 86: I/O port                                                                                 |  |

| WAIT     |                   | Input  | Wait: Signal used to request CPU bus wait.                                                        |  |

Table 2.2.2 Pin Names and Functions (2/6)

$\Diamond$

| Pin Name | Number<br>of Pins | I/O    | Functions                                                                                                     |  |

|----------|-------------------|--------|---------------------------------------------------------------------------------------------------------------|--|

| PA0      | 1                 | Output | Port A0: Output port (output "high" when initialized)                                                         |  |

| CAS0     |                   | Output | Column address strobe 0: Outputs CAS strobe for DRAM if address is within specified address area.             |  |

| LCAS0    |                   | Output | Lower column address strobe 0: Outputs lower CAS strobe for DRAM if address is within specified address area. |  |

| PA1      | 1                 | Output | Port A1: Output port (output "high" when initialized)                                                         |  |

| UCAS0    |                   | Output | Upper Column address strobe 0: Outputs upper CAS strobe for DRAM if address is within specified address area. |  |

| PA2      | 1                 | Output | Port A2: Output port (output "high" when initialized)                                                         |  |

| OE0      |                   | Output | Output enable 0: Outputs read enable signal for DRAM.                                                         |  |

| PA3      | 1                 | Output | Port A3: Output port (output "high" when initialized)                                                         |  |

| OE1      |                   | Output | Output enable 1: Outputs read enable signal for DRAM.                                                         |  |

| PA4      | 1                 | Output | Port A4: Output port (output "high" when initialized)                                                         |  |

| WE0      |                   | Output | Write enable 0: Outputs write enable signal for DRAM.                                                         |  |

| PB0      | 1                 | Output | Port B0: Output port (output "high" when initialized)                                                         |  |

| CAS1     |                   | Output | Column address strobe 1: Outputs CAS strobe for DRAM if address is within specified address area.             |  |

| LCAS1    |                   | Output | Lower column address strobe 1: Outputs lower CAS strobe for DRAM if address is within specified address area. |  |

| PB1      | 1                 | Output | Port B1: Output port (output "high" when initialized)                                                         |  |

| UCAS1    |                   | Output | Upper Column address strobe 1: Outputs upper CAS strobe for DRAM if address is within specified address area. |  |

| PB2      | 1                 | Output | Port B2: Output port (output "high" when initialized)                                                         |  |

| PB3      | 1                 | Output | Port B3: Output port (output "high" when initialized)                                                         |  |

| PB4      | 1                 | Output | Port B4: Output port (output "high" when initialized)                                                         |  |

| WE1      |                   | Output | Write enable 1: Outputs write enable signal for DRAM.                                                         |  |

### Table 2.2.3 Pin Names and Functions (3/6)

$\Diamond$

| Pin Name | Number<br>of Pins | I/O    | Functions                                                                            |

|----------|-------------------|--------|--------------------------------------------------------------------------------------|

| PC0      | 1                 | I/O    | Port C0: I/O port                                                                    |

| TO1      |                   | Output | Timer output 1: 8-bit timer 0 or 1 output                                            |

| TO7      |                   | Output | Timer output 7: 16-bit timer 7 output                                                |

| PC1      | 1                 | I/O    | Port C1: I/O port                                                                    |

| тоз      |                   | Output | Timer output 3: 8-bit timer 2 or 3 output                                            |

| тов      |                   | Output | Timer output B: 16-bit timer B output                                                |

| PD0      | 1                 | I/O    | Port D0: I/O port                                                                    |

| TO4      |                   | Output | Timer output 4: 16-bit timer 4 output                                                |

| PD1      | 1                 | I/O    | Port D1: I/O port                                                                    |

| TI4      |                   | Input  | Timer input 4: 16-bit timer 4 input                                                  |

| INT4     |                   | Input  | Interrupt request pin 4: Interrupt request pin with programmable rising/falling edge |

| PD2      | 1                 | I/O    | Port D2: I/O port                                                                    |

| TI5      |                   | Input  | Timer input 5: 16-bit timer 4 input                                                  |

| INT5     |                   | Input  | Interrupt request pin 5: Interrupt request pin with rising edge                      |

| PD4      | 1                 | I/O    | Port D4: I/O port                                                                    |

| TO6      |                   | Output | Timer output 6: 16-bit timer 6 output                                                |

| PD5      | 1                 | I/O    | Port D5: I/O port                                                                    |

| ТІ6      |                   | Input  | Timer input 6: 16-bit timer 6 input                                                  |

| INT6     |                   | Input  | Interrupt request pin 6: Interrupt request pin with programmable rising/falling edge |

| PD6      | 1                 | I/O    | Port D6: I/O port                                                                    |

| TI7      |                   | Input  | Timer input 7: 16-bit timer 6 input                                                  |

| INT7     |                   | Input  | Interrupt request pin 7: Interrupt request pin with rising edge                      |

| PE0      | 1                 | I/O    | Port E0: I/O port                                                                    |

| TO8      |                   | Output | Timer output 8: 16-bit timer 8 output                                                |

| PE1      | 1                 | I/O    | Port E1: I/O port                                                                    |

| TI8      |                   | Input  | Timer input 8: 16-bit timer 8 input                                                  |

| INT8     |                   | Input  | Interrupt request pin 8:/Interrupt request pin with programmable rising/falling edge |

| PE2      | 1                 | I/O    | Port E2: I/O port                                                                    |

| ТI9      |                   | Input  | Timer input 9: 16-bit-timer 8 input                                                  |

| INT9     |                   | Input  | Interrupt request pin 9: Interrupt request pin with rising edge                      |

| PE4      | 1                 | I/O    | Port E4: I/Q port                                                                    |

| ТОА      |                   | Output | Timer output A: 16-bit timer A output                                                |

| PE5      | 1                 | I/O    | Port E5: I/O port                                                                    |

| TIA      |                   | Input  | Timer input A 16-bit timer A input                                                   |

| INTA     |                   | Input  | Interrupt request pin A: Interrupt request pin with programmable rising/falling edge |

| PE6      | 1                 | I/O    | Port E6: I/O port                                                                    |

| TIB      |                   | Input  | Timer input B: 16-bit timer A input                                                  |

| INTB     |                   | Input  | Interrupt request pin B: Interrupt request pin with rising edge                      |

| Table 2.2.4 | Pin Names and Functions ( | (4/6)  |

|-------------|---------------------------|--------|

| 10010 2.2.1 |                           | ( 1/0) |

| Pin Name   | Number<br>of Pins | I/O    | Functions                                                                                           |

|------------|-------------------|--------|-----------------------------------------------------------------------------------------------------|

| PF0        | 1                 | I/O    | Port F0: I/O port                                                                                   |

| TXD0       |                   | Output | Serial send data 0                                                                                  |

| PF1        | 1                 | I/O    | Port F1: I/O port                                                                                   |

| RXD0       |                   | Input  | Serial receive data 0                                                                               |

| PF2        | 1                 | I/O    | Port F2: I/O port                                                                                   |

| CTS0       |                   | Input  | Serial data receive enable 0                                                                        |

| SCLK0      |                   | I/O    | Serial clock I/O 0                                                                                  |

| PF4        | 1                 | I/O    | Port F4: I/O port                                                                                   |

| TXD1       |                   | Output | Serial send data 1                                                                                  |

| PF5        | 1                 | I/O    | Port F5: I/O port                                                                                   |

| RXD1       |                   | Input  | Serial receive data 1                                                                               |

| PF6        | 1                 | I/O    | Port F6: I/O port                                                                                   |

| CTS1       |                   | Input  | Serial data receive enable 1                                                                        |

| SCLK1      |                   | I/O    | Serial clock I/O 1                                                                                  |

| PG0 to PG7 | 8                 | Input  | Port G: Input port                                                                                  |

| AN0 to AN7 |                   | Input  | Analog input: Input to 10-bit AD converter                                                          |

| DAOUT0     | 1                 | Output | DA output 0: Output from 8-bit DA converter 0                                                       |

| DAOUT1     | 1                 | Output | DA output 1: Output from 8-bit DA converter 1                                                       |

| PH0        | 1                 | I/O    | Port H0: I/O port                                                                                   |

| TC0        |                   | Output | Terminal count 0: Outputs "high" strobe when counter value of micro-DMA channel 0 is "0".           |

| PH1        | 1                 | I/O    | Port H1: I/O port                                                                                   |

| TC1        |                   | Output | Terminal count 1: Outputs "high" strobe when counter value of micro-DMA channel 1 is "0".           |

| PH2        | 1                 | I/O    | Port H2: I/O port                                                                                   |

| TC2        |                   | Output | Terminal count 2: Outputs "high" strobe when counter value of micro-DMA channel 2 is "0".           |

| PH3        | 1                 | I/O    | Port H3: I/O port                                                                                   |

| TC3        |                   | Output | Terminal count 3: Outputs //high" strobe when counter value of micro-DMA channel 3 is "0".          |

| PH4        | 1                 | I/O    | Port H4: I/O port (schmitt input)                                                                   |

| INT0       |                   | Input  | Interrupt request pin 0: Interrupt request pin with programmable level/rising edge. (schmitt input) |

| PZ0 to PZ7 | 8                 | I/O    | Port Z: I/O port                                                                                    |

| NMI        | 1                 | Input  | Non-maskable interrupt request pin: Interrupt request pin with falling edge.                        |

|            |                   |        | Can also be operated at rising edge by program. (schmitt input)                                     |

| WDTOUT     | 1                 | Output | Watchdog timer output pin                                                                           |

Table 2.2.5 Pin Names and Functions (5/6)

$\bigcirc$

| Pin Name | Number<br>of Pins | I/O    | Functions                                                      |  |

|----------|-------------------|--------|----------------------------------------------------------------|--|

| AM0, 1   | 2                 | Input  | Address mode: Selects external data bus width.                 |  |

|          |                   |        | AM1 = "low" AM0 = "low": Start with 8-bit external data bus    |  |

|          |                   |        | AM1 = "low" AM0 = "high": Start with 16-bit external data bus  |  |

|          |                   |        | AM1 = "high" AM0 = "low": Don't use this setting               |  |

|          |                   |        | AM1 = "high" AM0 = "high": Don't use this setting              |  |

| TEST0, 1 | 2                 | Input  | Test: Input "low" when using                                   |  |

| CLK      | 1                 | Output | Clock output: Outputs system clock                             |  |

| X1/X2    | 2                 | I/O    | Oscillator connecting pin                                      |  |

| RESET    | 1                 | Input  | Reset: Initializes LSI (with pull-up resistor) (schmitt input) |  |

| VREFH    | 1                 | Input  | Pin for reference voltage input to AD converter ("high" level) |  |

| VREFL    | 1                 | Input  | Pin for reference voltage input to AD converter ("low" level   |  |

| DAREFH   | 1                 | Input  | Pin for reference voltage input to DA converter ("high" level) |  |

| DAREFL   | 1                 | Input  | Pin for reference voltage input to DA converter ("low" level)  |  |

| ADVCC    | 1                 | -      | Power supply pin for 10-bit AD converter                       |  |

| ADVSS    | 1                 | -      | GND pin for 10-bit AD converter (0 V)                          |  |

| DAVCC    | 1                 | -      | Power supply pin for 8-bit DA converter                        |  |

| DAVSS    | 1                 | -      | GND pin for 8-bit DA converter (0 V)                           |  |

| CLVCC    | 1                 | -      | Power supply pin for clock doubler                             |  |

| CLVSS    | 1                 | -      | GND pin for clock doubler                                      |  |

| DVCC     | 8                 | T      | Power supply pin (+5 V) (Connect all DVCC pins to +5V)         |  |

| DVSS     | 8                 | -      | GND pin (0 V) (Connect all DVSS pins to GND(0)).)              |  |

Table 2.2.6 Pin Names and Functions (6/6)

$\Diamond$

## 3. Operation

The following is a block-by-block description of the functions and basic operation of TMP94C251A.

3.1 CPU

TMP94C251A contains an advanced, high-speed 32-bit CPU (900/H2 CPU).

### 3.1.1 CPU Outline

900/H2 CPU is high-speed and high-performance CPU based on 900/H CPU. 900/H2 CPU has expanded 32-bit internal data bus to process instructions more quickly. Functional differences between 900/H2 CPU and 900/H CPU are as follows;

|                                        | 900/H2 CPU                                         |

|----------------------------------------|----------------------------------------------------|

| Width of CPU Address Bus               | 24-bit                                             |

| Width of CPU Data Bus                  | 32-bit                                             |

| Internal Operating Frequency           | 20 MHz                                             |

| Minimum Bus Cycle                      | 1-clock access<br>(50 ns @ 20 MHz)                 |

| <b>Bus Sizing Function</b>             | 8/16-bit                                           |

| Internal RAM                           | 32-bit 1-clock access                              |

| Internal I/O                           | 8/16/32-bit 2-clock access                         |

| External Device                        | 8/16-bit 2-clock access<br>(can insert some waits) |

| Minimum Instruction<br>Execution Cycle | 1-clock<br>(50 ns @20 MHz)                         |

| Conditional Jump                       | 2-clock<br>(100 ns @20 MHz)                        |

| Instruction Queue Buffer               | 12-byte                                            |

| Instruction Set                        | No MIN instruction<br>No LDX instruction           |

| CPU mode                               | No MIN (minimum) mode                              |

| Micro DMA                              | 8-channel                                          |

$\langle \rangle$

### 3.1.2 Reset Operation

When resetting the TMP94C251A microcontroller, ensure that the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then set the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks (2 µs at 10 MHz). Thus, when turn on the switch, be set to the power supply voltage is within the operating voltage range, and that the internal high-frequency oscillator has stabilized. Then hold the  $\overline{\text{RESET}}$  input to low level at least for 10 system clocks.

Clock gear is initialized 1/16 mode by reset operation. It means that the system clock mode fsys is set to fc/32 (=  $fc/16 \times 1/2$ ).

When the reset is accepted, the CPU:

- Set the program counter (PC) to the reset vector stored at addresses FFFF00H to FFFF02H.

- PC (7:0)  $\leftarrow$  Value at address FFFF00H

- PC (15:8)  $\leftarrow$  Value at address FFFF01H

- PC (23:16)  $\leftarrow$  Value at address FFFF02H

- Sets the stack pointer (XSP) to 00000000H

- Sets bits IFF2 to IFF0 of the status register (SR) to 11/1 This sets the interrupt level mask register to level 7).

- Clears bits RFP1 to RFP0 of the status register (SR) to 00 (This sets the register banks to 0).

After reset is released, the CPU begins execution from the instruction at the location specified in the PC. Other than the changes described above, reset does not alter any internal CPU registers.

When reset is accepted, processing of the internal I/O, port, and other pins are as follows:

- Initializes the internal I/O registers as table of "Special Function Register" in section 5.

- Set ports pins to general purpose input port mode.

- Sets the WDTOUT pin to "Dow". (However, when reset is released, sets to "High".)

When external reset is released, built-in clock doubler begins operation and after the stable time (1.6384 ms at 20 MHz) elapse of the circuit, internal reset is released.

The operation of memory controller and DRAM controller cannot be insured until power supply becomes stable after power-on reset. The external RAM data provided before turning on the TMP94C251A may be spoiled because the control signals are unstable until power supply becomes stable after power on reset.

### 3.1.3 Data Bus Size after Reset Release

The start data bus size is determined depending on the state of a AM1/AM0 pins just after reset release. Then the external memory is accessed as follows.

| AM1 | AM0 | Start mode              |  |

|-----|-----|-------------------------|--|

| "0" | "0" | 8 bit data bus (1wait)  |  |

| "0" | "1" | 16 bit data bus (1wait) |  |

| "1" | "0" | Don't use this setting  |  |

| "1" | "1" | Don't use this setting  |  |

For the details, refer to chapter 3.6 "Memory Controller".

### 3.1.4 Setting of TEST0, TEST1

Connect TEST0, TEST1 pin to "GND" to use.

### 3.2 Memory Map

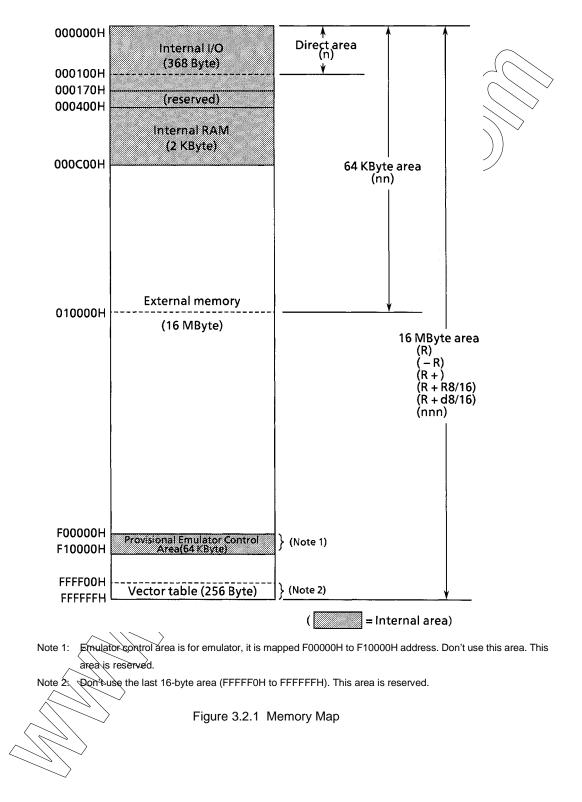

Figure 3.2.1 is a memory map of the TMP94C251A.

>

### 4. Electrical Characteristics

### 4.1 Maximum Ratings

| Symbol         | Parameter                     | Rating             | Unit |

|----------------|-------------------------------|--------------------|------|

| V cc           | Power Supply Voltage          | – 0.5 to 6.5       | V    |

| VIN            | Input Voltage                 | - 0.5 to Vcc + 0.5 | V    |

| Σ I <b>O</b> L | Output Current (total)        | 120                | mA   |

| ΣΙΟΗ           | Output Current (total)        | - 120              | mA   |

| PD             | Power Dissipation (Ta = 70°C) | 600                | mW   |

Note: The maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no maximum rating value will ever be exceeded.

### 4.2 DC Electrical Characteristics

Vcc = 5 V  $\pm$  10%, TA = -20 to 70°C X1 = 8 to 10 MHz (Internal operation = 16 to 20 MHz)

| Symbol | Parameter                                                                                                                                                                                                     | Min   | Max       | Unit | Test Condition |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|------|----------------|

| V ILO  | Input Low Voltage<br>P00 to P07 (D0 to 7)<br>P10 to P17 (D8 to 15)<br>P20 to P27 (D16 to 23)<br>P30 to P37 (D24 to 31)                                                                                        | - 0.3 | 0.8       | V    |                |

| V IL1  | Input Low Voltage<br>P40 to P47<br>P50 to P57<br>P60 to P67<br>P75<br>P86<br>PC0, PC1<br>PD0 to PD2, PD4 to PD6<br>PE0 to PE2, PE4 to PE6<br>PF0 to PF2, PF4 to PF6<br>PG0 to PG7<br>PH0 to PH3<br>PZ0 to PZ7 | - 0.3 | 0.3*Vcc   | V    |                |

| V IL2  | Input Low Voltage<br>PH4 (INT0)<br>NMI<br>RESET                                                                                                                                                               | - 0.3 | 0.25*Vcc  | V    |                |

| V IL3  | Input Low Voltage<br>AM0, AM1<br>TEST0, TEST1                                                                                                                                                                 | - 0.3 | 0.3       | V    |                |

| V IL4  | Input Low Voltage<br>X1                                                                                                                                                                                       | - 0.3 | 0.2*Vcc   |      |                |

| V IHO  | Input High Voltage<br>P00 to P07 (D0 to 7)<br>P10 to P17 (D8 to 15)<br>P20 to P27 (D16 to 23)<br>P30 to P37 (D24 to 31)                                                                                       | 2.2   | Vcc + 0.3 | V    |                |

Note: Typical value are for  $Ta = 25 \circ C$  and  $Vcc = 5 \vee U$  unless otherwise noted.

| Symbol | Parameter                                                                                                                                                                                                      | Min         | Max       | Unit | Test Condition                                    |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------|------|---------------------------------------------------|

| V IH1  | Input High Voltage<br>P40 to P47<br>P50 to P57<br>P60 to P67<br>P75<br>P86<br>PC0, PC1<br>PD0 to PD2, PD4 to PD6<br>PE0 to PE2, PE4 to PE6<br>PF0 to PF2, PF4 to PF6<br>PG0 to PG7<br>PH0 to PH3<br>PZ0 to PZ7 | 0.7*Vcc     | Vcc + 0.3 | V    |                                                   |

| V IH2  | Input High Voltage<br><u>PH4</u> (INTO)<br><u>NMI</u><br>RESET                                                                                                                                                 | 0.75*Vcc    | Vcc + 0.3 | V    |                                                   |

| V IH3  | Input High Voltage<br>AM0, AM1<br>TEST0, TEST1                                                                                                                                                                 | Vcc-0.3     | Vcc + 0.3 | V    |                                                   |

| VIH4   | Input High Voltage<br>X1                                                                                                                                                                                       | 0.8*Vcc     | Vcc + 0.3 | V    |                                                   |

| V OL   | Output Low Voltage                                                                                                                                                                                             |             | 0.45      | V    | IOL = 1.6 mA                                      |

| V OH0  | Operating Cururent (NORMAL)                                                                                                                                                                                    | 2.4         |           | V    | IOH = - 400µA                                     |

| V OH1  | Output High Voltage                                                                                                                                                                                            | 0.75*Vcc    |           | V    | IOH = - 100μA                                     |

| V OH2  | Output High Voltage                                                                                                                                                                                            | 0.9*Vcc     |           | V    | IOH = - 20μA                                      |

| I LI   | Input Leakage Current                                                                                                                                                                                          | 0.02 (typ.) | ±5        | μA   | 0.0V≦Vin≦Vcc                                      |

| I LO   | Output Leakage Current                                                                                                                                                                                         | 0.05 (typ.) | ± 10      | μA   | 0.2V≦ Vin≦ Vcc – 0.2 V                            |

| l cc0  | Operating Current (NORMAL)                                                                                                                                                                                     | 90          | 108       | mA   | X1 = 10 MHz<br>(Internal 20 MHz)                  |

| l cc1  | RUN                                                                                                                                                                                                            | 50          | 70        | mA   | X1 = 10 MHz<br>(Internal 20 MHz)                  |

| l cc2  | IDLE                                                                                                                                                                                                           | 5           | 20        | mA   | X1 = 10 MHz<br>(Internal 20 MHz)                  |

| l cc3  | STOP                                                                                                                                                                                                           | 0.5         | 50        | μA   | $0.2 V \le Vin \le Vcc - 0.2 V$<br>Ta = - 20~70°C |

| l cc4  | STOP                                                                                                                                                                                                           |             | 10        | μA   | $0.2 V \le Vin \le Vcc - 0.2 V$<br>Ta = 0~50°C    |

| V STOP | Power Down Voltage @ STOP<br>(for internal RAM back-up)                                                                                                                                                        | 2.0         | 6.0       | V    | VIL2 = 0.2*Vcc<br>VIH2 = 0.8*Vcc                  |

| RRST   | Pu <u>ll Up</u> Registance<br>RESET                                                                                                                                                                            | 50          | 150       | kΩ   |                                                   |

| CIO    | Pin Capacitance                                                                                                                                                                                                |             | 10        | pF   | fc = 1 MHz                                        |

| VTH    | Schmitt Width<br>PH4 (INTO)<br>NMI<br>RESET                                                                                                                                                                    | 0.4         | 1.0 (typ) | V    |                                                   |

#### **AC Electrical Characteristics** 4.3

#### Basic Bus Cycle 4.3.1

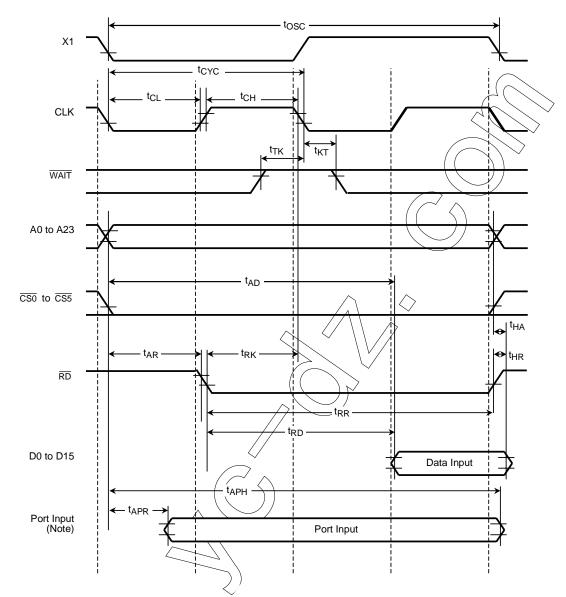

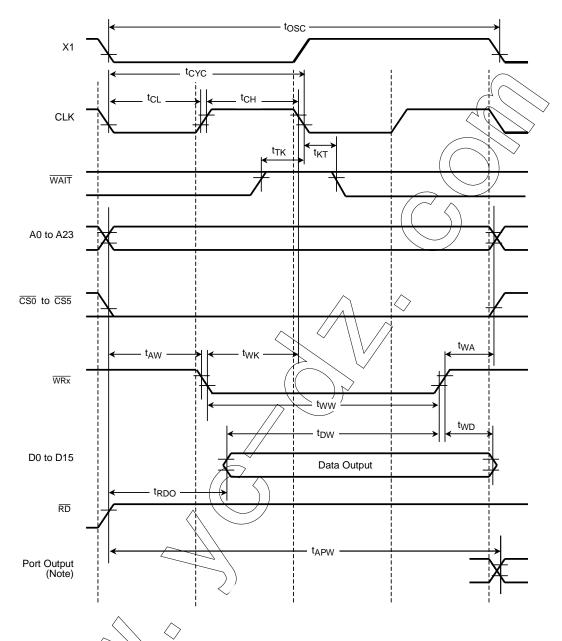

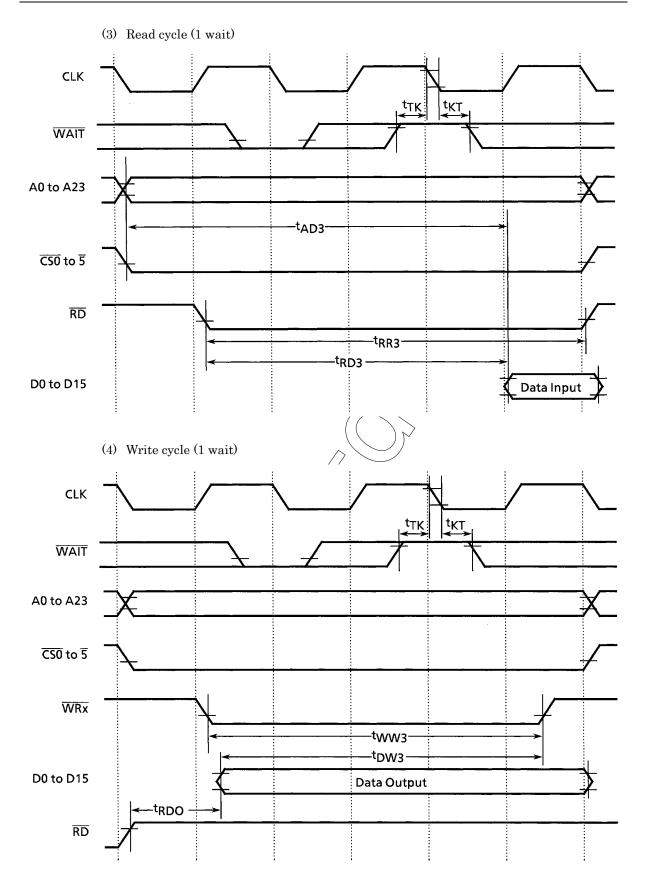

### (1) Read cycle

| No. | Symbol           | Parameter                                                     | Min                 | Max              | at 20 MHz | at 16∕ <i>M</i> Hz | Unit |

|-----|------------------|---------------------------------------------------------------|---------------------|------------------|-----------|--------------------|------|

| 1   | tosc             | OSC period (X1/X2)                                            | 100                 | 125              | 100       | 125                | ns   |

| 2   | tCYC             | System Clock Period (= T)                                     | 50                  | 62.5             | 50        | 62.5               | ns   |

| 3   | t <sub>CL</sub>  | CLK Low Width                                                 | 0.5 	imes T - 15    |                  | 10        | 16                 | ∕ns  |

| 4   | t <sub>CH</sub>  | CLK High Width                                                | $0.5 \times T - 15$ |                  | 10        | 16                 | ns   |

| 5-1 | t <sub>AD</sub>  | A0 to A23 $\rightarrow$ D0 to D31 Input at 0 waits            |                     | $2.0\times T-50$ | 50        | \75 <sup>°</sup>   | ns   |

| 5-2 | t <sub>AD3</sub> | A0 to A23 $\rightarrow$ D0 to D31 Input at 1 wait             |                     | 3.0 	imes T - 50 | 100       | 138                | ns   |

| 6-1 | t <sub>RD</sub>  | $\overline{RD}$ Fall $\rightarrow$ D0 to D31 Input at 0 waits |                     | 1.5 	imes T - 45 | 30        | 49                 | ns   |

| 6-2 | t <sub>RD3</sub> | $\overline{RD}$ Fall $\rightarrow$ D0 to D31 Input at 1 wait  |                     | $2.5\times T-45$ | 80        | 111                | ns   |

| 7-1 | t <sub>RR</sub>  | RD Low Width at 0 waits                                       | 1.5 	imes T - 20    |                  | 55)       | 74                 | ns   |

| 7-2 | t <sub>RR3</sub> | RD Low Width at 1 wait                                        | $2.5\times T-20$    |                  | 105       | 136                | ns   |

| 8   | t <sub>AR</sub>  | A0 to A23 Valid $\rightarrow \overline{RD}$ Fall              | $0.5 \times T - 20$ |                  | 5         | 11                 | ns   |

| 9   | t <sub>RK</sub>  | $\overline{RD}$ Fall $\rightarrow CLK$ Fall                   | $0.5 \times T - 20$ |                  | 5         | 11                 | ns   |

| 10  | t <sub>HA</sub>  | A0 to A23 Invalid $\rightarrow$ D0 to D31 Hold                | 0                   | $\sim$ $\sim$    | 0         | 0                  | ns   |

| 11  | t <sub>HR</sub>  | $\overline{\text{RD}}$ Rise $\rightarrow$ D0 to D31 Hold      | 0                   |                  | 0         | 0                  | ns   |

| 12  | t <sub>APR</sub> | A0 to A23 Valid $\rightarrow$ PORT Input                      | ~ []                | 2.0 × T -/120    | -20       | 5                  | ns   |

| 13  | t <sub>APH</sub> | A0 to A23 Valid $\rightarrow$ PORT Hold                       | 2.0 × T             |                  | 100       | 125                | ns   |

| 14  | t <sub>TK</sub>  | WAIT Setup Time                                               | 45                  |                  | 15        | 15                 | ns   |

| 15  | t <sub>KT</sub>  | WAIT Hold Time                                                | 5                   |                  | 5         | 5                  | ns   |

|     |                  | (2) Write cycle                                               | $\gamma \bigcirc$   | )                |           |                    |      |

### (2) Write cycle

| No. | Symbol           | Parameter                                                      | Min                  | Max              | at 20 MHz | at 16 MHz | Unit |

|-----|------------------|----------------------------------------------------------------|----------------------|------------------|-----------|-----------|------|

| 1   | tosc             | OSC Period (X1/X2)                                             | 100                  | 125              | 100       | 125       | ns   |

| 2   | tCYC             | System Clock Period (= T)                                      | 50                   | 62.5             | 50        | 62.5      | ns   |

| 3   | t <sub>CL</sub>  | CLK Low Width                                                  | $0.5 \times T - 15$  |                  | 10        | 16        | ns   |

| 4   | t <sub>CH</sub>  | CLK High Width                                                 | $0.5 \times T - 15$  |                  | 10        | 16        | ns   |

| 5-1 | t <sub>DW</sub>  | D0 to D31 Valid $\rightarrow \overline{WRx}$ Rise at $@$ waits | $1.25 \times T - 35$ |                  | 28        | 43        | ns   |

| 5-2 | t <sub>DW3</sub> | D0 to D31 Valid $\rightarrow \overline{WRx}$ Rise at 1 wait    | $2.25 \times T - 35$ |                  | 78        | 106       | ns   |

| 6-1 | t <sub>WW</sub>  | WRx Low Width at 0 waits                                       | $1.25 \times T - 30$ |                  | 33        | 48        | ns   |

| 6-2 | t <sub>WW3</sub> | WRx Low Width at 1 wait                                        | $2.25\times T-30$    |                  | 83        | 111       | ns   |

| 7   | t <sub>AW</sub>  | A0 to A23 Valid $\rightarrow \overline{WRx}$ Fall              | $0.5\times T-20$     |                  | 5         | 11        | ns   |

| 8   | t <sub>WK</sub>  | $\overline{WRx} \; Fall \to CLK \; Fall$                       | $0.5\times T-20$     |                  | 5         | 11        | ns   |

| 9   | t <sub>WA</sub>  | $\overline{\text{WRx}}$ Rise $\rightarrow AO$ to A23 Hold      | $0.25 \times T - 5$  |                  | 8         | 11        | ns   |

| 10  | t <sub>WD</sub>  | WRx Rise -> DO to D31 Hold                                     | $0.25 \times T - 5$  |                  | 8         | 11        | ns   |

| 11  | t <sub>APW</sub> | A0 to A23 Valid PORT, Output                                   |                      | 2.0 	imes T + 70 | 170       | 195       | ns   |

| 12  | t <sub>TK</sub>  | WAIT Setup Time                                                | 15                   |                  | 15        | 15        | ns   |

| 13  | t <sub>KT</sub>  | WAIT Hold Time                                                 | 5                    |                  | 5         | 5         | ns   |

| 14  | t <sub>RDO</sub> | RD Rise > Do to D15 Output                                     | 0.5 	imes T - 5      |                  | 20        | 26        | ns   |

AC Condition

Input:

Output: P0 to P3 (D0 to D31), P4 to P6 (A0 to A23), P70 (RD), P71 to P74 (WRx)

High = 2.0 V, Low = 0.8 V, CL = 50 pF

High = 2.4 V, Low =

$$0.45$$

V

Others

High = 0.8 Vcc, Low = 0.2 Vcc

(1) Read cycle (0 waits)

- Note 1: The phase relation between X1 input signal and the other signals is unsettled. The timing chart above is an example.

- Note 2: Since the CPU accesses the internal area to read data from a port, the control signals of external pins such as RD and CS are not enabled. Therefore, the above waveform diagram should be regarded as depicting internal operation. Please also note that the timing and AC characteristics of port input/output shown above are typical representation. For details, contact your local Toshiba sales representative.

(2) Write cycle (0 waits)

- Note 1: The phase relation between X1 input signal and the other signals is unsettled. The timing chart above is an example.

- Note 2: WRx shows WRL, WRH.

- Note 3: Since the CPU accesses the internal area to write data to a port, the control signals of external pins such as WR and CS are not enabled. Therefore, the above waveform diagram should be regarded as depicting internal operation. Please also note that the timing and AC characteristics of port input/output shown above are typical representation. For details, contact your local Toshiba sales representative.

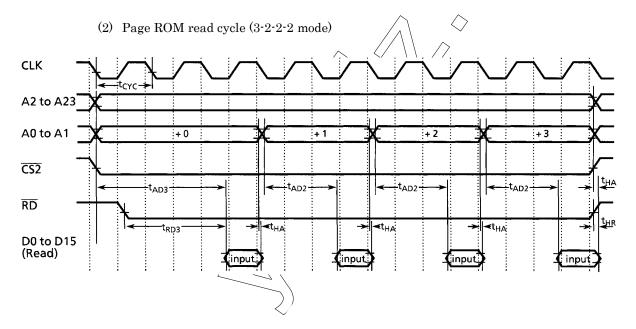

### 4.3.2 Page ROM Read Cycle

| No. | Symbol           | Parameter                                                 | Min | Max        | @20 MHz | @16 MHz | Unit |

|-----|------------------|-----------------------------------------------------------|-----|------------|---------|---------|------|

| 1   | tcyc             | System Clock Period ( = T)                                | 50  | 62.5       | 50      | 62.5    | ns   |

| 2   | t <sub>AD2</sub> | A0, A1 $\rightarrow$ D0 to D15 Input                      |     | 1.0 × T-50 | 50      | 75      | ns   |

| 3   | t <sub>AD3</sub> | A2 to A23 $\rightarrow$ D0 to D15 Input                   |     | 3.0×T-50   | 100     | 138     | ns   |

| 4   | t <sub>RD3</sub> | $\overline{\text{RD}}$ Fall $\rightarrow$ D0 to D15 Input |     | 2.5×T-45   | 80      | 111     | ns   |

| 5   | t <sub>HA</sub>  | A0 to A23 Invalid $\rightarrow$ D0 to D15 Hold            | 0   |            | 0       | 0       | ns   |

| 6   | t <sub>HR</sub>  | $\overline{\text{RD}}$ Rise $\rightarrow$ D0 to D15 Hold  | 0   |            | 0       | 0       | ns   |

### (1) $3-2-2-2 \mod 2$

### AC Condition

Output: P4 to P6 (A0 to A23), P70 ( RD )

High = 2.0 V, Low = 0.8 V, CL = 50 pF CLK, P82 ( $\overline{CS2}$ ) High = 2.0 V, Low = 0.8 V, CL = 50 pF Input: P0 to P1 (D0 to D15) High = 2.4 V, Low = 0.45 V

$\langle \rangle$

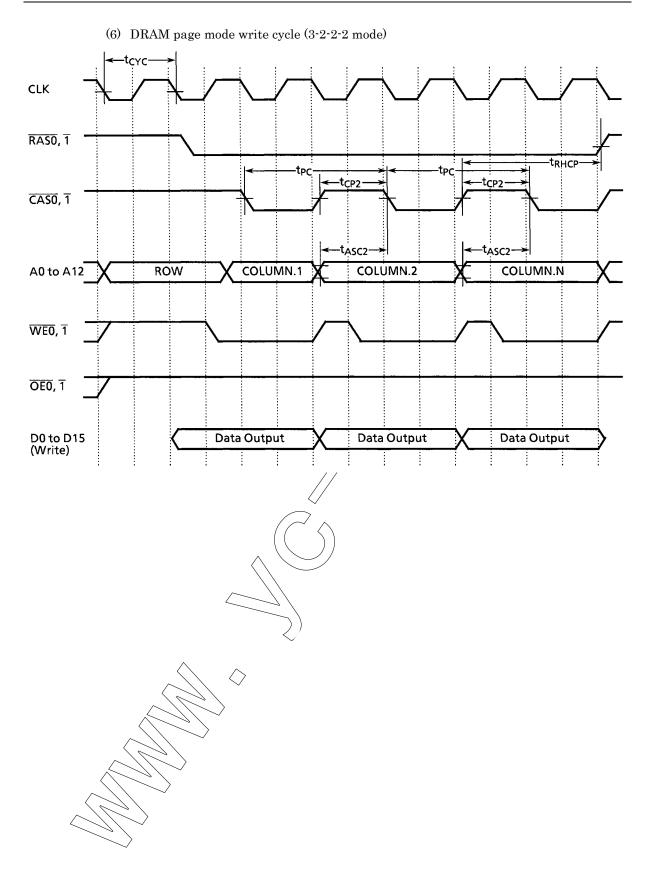

| No.  | Symbol            | Parameter                                      | Min                 | Max               | @ 20 MHz | @ 16 MHz | Unit |

|------|-------------------|------------------------------------------------|---------------------|-------------------|----------|----------|------|

| 1    | tCYC              | System Clock Period (= T)                      | 50                  | 62.5              | 50       | 62.5     | ns   |

| 2    | t <sub>RC</sub>   | RAS Cycle Time                                 | 3.00 	imes T        |                   | 150      | 188      | ns   |

| 3    | t <sub>PC</sub>   | Page Mode Cycle Time                           | 2.00 × T            |                   | 100      | 125      | ns   |

| 4-1  | tRAC              | RAS Access Time                                |                     | 1.75 × T – 45     | 43       | 64       | ns   |

| 4-2  | t <sub>RAC4</sub> | RAS Access Time @ 4 Clock Access               |                     | 2.75 	imes T - 45 | 93       | 127      | ns   |

| 5    | tCAC              | CAS Access Time                                |                     | 1.00 	imes T - 40 | 10       | (23)     | ns   |

| 6-1  | t <sub>AA</sub>   | Column Address Access Time                     |                     | 1.25 	imes T - 45 | 18       | 33       | ns   |

| 6-2  | t <sub>AA2</sub>  | Column Address Access Time<br>@ Page Mode      |                     | $2.00\times T-45$ | 55       | 80       | ns   |

| 6-3  | t <sub>AA4</sub>  | Column Address Access Time<br>@ 4 Clock Access |                     | 2.25 × T – 45     | 68       | 96       | ns   |

| 7    | t <sub>CPA</sub>  | CAS Pre-charge Access Time                     |                     | 2.00 × T – 45/    | 55       | 80       | ns   |

| 8    | tOFF              | Input Data Hold Time                           | 0                   | (                 | ( 0))    | 0        | ns   |

| 9    | t <sub>RP</sub>   | RAS Pre-charge Time                            | 1.25 × T – 20       |                   | 43       | 58       | ns   |

| 10-1 | t <sub>RAS</sub>  | RAS Width                                      | 1.75 × T – 20       |                   | 68       | 89       | ns   |

| 10-2 | t <sub>RAS4</sub> | RAS Width @ 4 Clock Access                     | 2.75 × T – 20       |                   | 118      | 152      | ns   |

| 11   | t <sub>RSH</sub>  | RAS Hold Time                                  | 1.00 × T – 20       | ~ ^               | 30       | 43       | ns   |

| 12   | tRHCP             | CAS Pre-charge to RAS Hold Time                | 2.00 × T – 20       | $ \uparrow $      | 80       | 105      | ns   |

| 13-1 | tCSH              | CAS Hold Time                                  | 1.75 × T ≠ 20       | $   \land$        | 68       | 89       | ns   |

| 13-2 | tCSH4             | CAS Hold Time @ 4 Clock Access                 | 2.75 × T – 20       |                   | 118      | 152      | ns   |

| 14   | t <sub>CAS</sub>  | CAS Width                                      | 1.00×T-20           | 17                | 30       | 43       | ns   |

| 15   | t <sub>RCD</sub>  | RAS – CAS Delay Time                           | 0/75 × T - 17       |                   | 21       | 30       | ns   |

| 16   | t <sub>RAD</sub>  | RAS – Column Address Delay Time                | $(\langle \rangle)$ | 0.50 × T + 20     | 45       | 51       | ns   |

| 17   | tCRP              | CAS – RAS Pre-charge Time                      | ).25 × T - 20       |                   | 43       | 58       | ns   |

| 18-1 | t <sub>CP</sub>   | CAS Pre-charge Time @ Refresh                  | 0.50 × T – 15       |                   | 10       | 16       | ns   |

| 18-2 | t <sub>CP2</sub>  | CAS Pre-charge Time @ Page Mode                | 1.00 	imes T - 20   |                   | 30       | 43       | ns   |

| 19   | t <sub>ASR</sub>  | Row Address Set-up Time                        | 1.25 × T – 40       |                   | 23       | 38       | ns   |

| 20   | t <sub>RAH</sub>  | Row Address Hold Time                          | 0.50 × T – 15       |                   | 10       | 16       | ns   |

| 21-1 | tASC              | Column Address Set-up Time                     | 0.25 × T – 12       |                   | 1        | 4        | ns   |

| 21-2 | t <sub>ASC2</sub> | Column Address Set-up Time<br>@ Page Mode      | 1.00 	imes T - 20   |                   | 30       | 43       | ns   |

| 22   | t <sub>CAH</sub>  | Column Address Hold Time                       | 1.00 × T – 20       |                   | 30       | 43       | ns   |

| 23   | t <sub>AR</sub>   | Column Address Hold Time from RAS              | 1.75 × T – 20       |                   | 68       | 89       | ns   |

| 24   | t <sub>RAL</sub>  | Column Address RAS Read Time                   | 1.25 × T – 20       |                   | 43       | 58       | ns   |

| 25   | t <sub>RCS</sub>  | Read Command Set-up Time                       | 2.00 	imes T - 40   |                   | 60       | 85       | ns   |

|      | t <sub>RCH</sub>  | Read Command Hold Time from CAS                | 0.50 	imes T - 20   |                   | 5        | 11       | ns   |

|      | t <sub>RRH</sub>  | Read Command Hold Time from RAS                | 0.50 	imes T - 20   |                   | 5        | 11       | ns   |

|      | tWCH              | Write Command Hold Time                        | 1.00 × T – 20       |                   | 30       | 43       | ns   |

|      | tWCR              | Write Command Hold Time from RAS               | 1.75 × T – 20       |                   | 68       | 89       | ns   |

|      | t <sub>WP</sub>   | Write Command Time                             | 1.50 × T – 20       |                   | 55       | 74       | ns   |

|      |                   | Write Command RAS Read Time                    | 1.50 	imes T - 20   |                   | 55       | 74       | ns   |

| 32   | tCWL              | Write Command CAS Read Time                    | 1.50 × T – 20       |                   | 55       | 74       | ns   |

| 33   |                   | Data Output Set-up Time                        | 1.50 × T – 30       |                   | 45       | 58       | ns   |

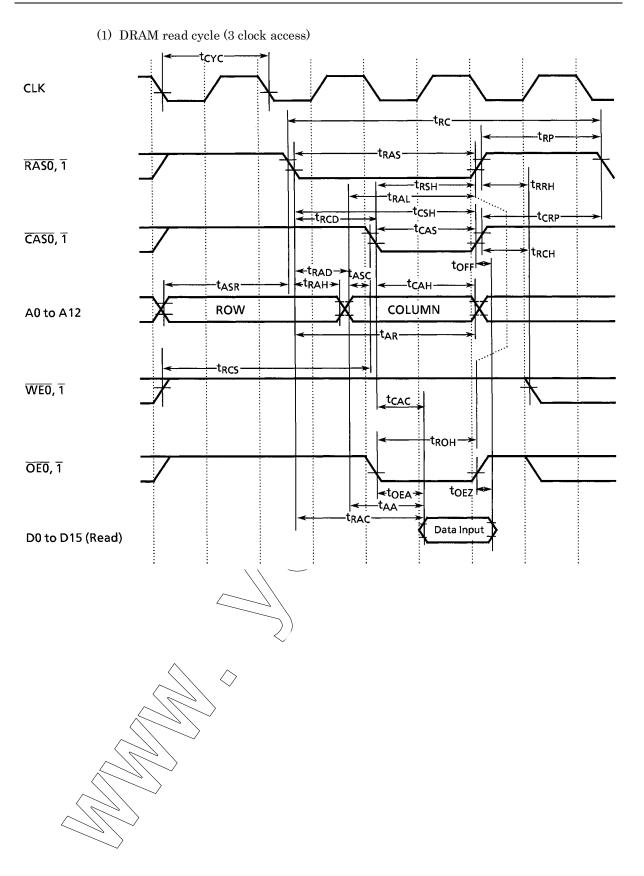

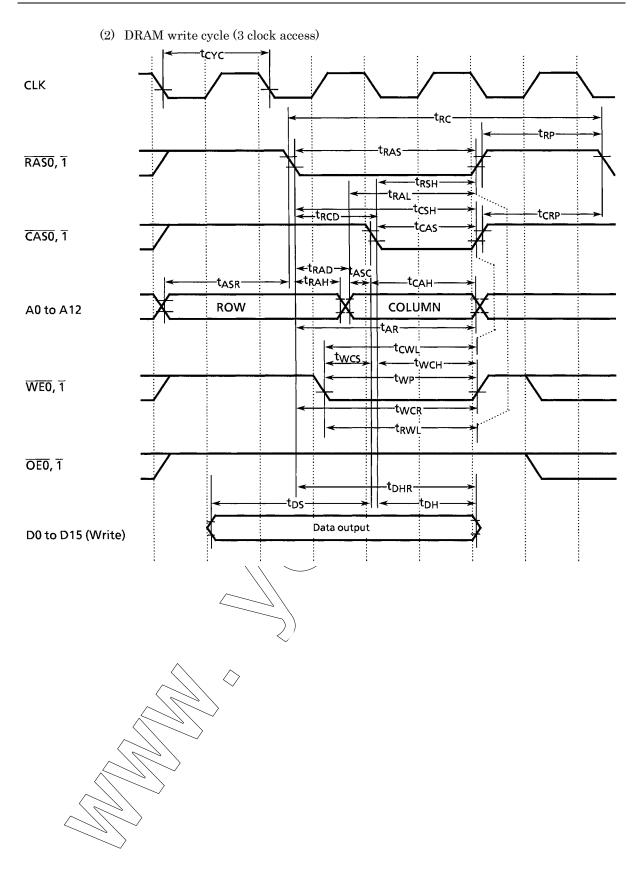

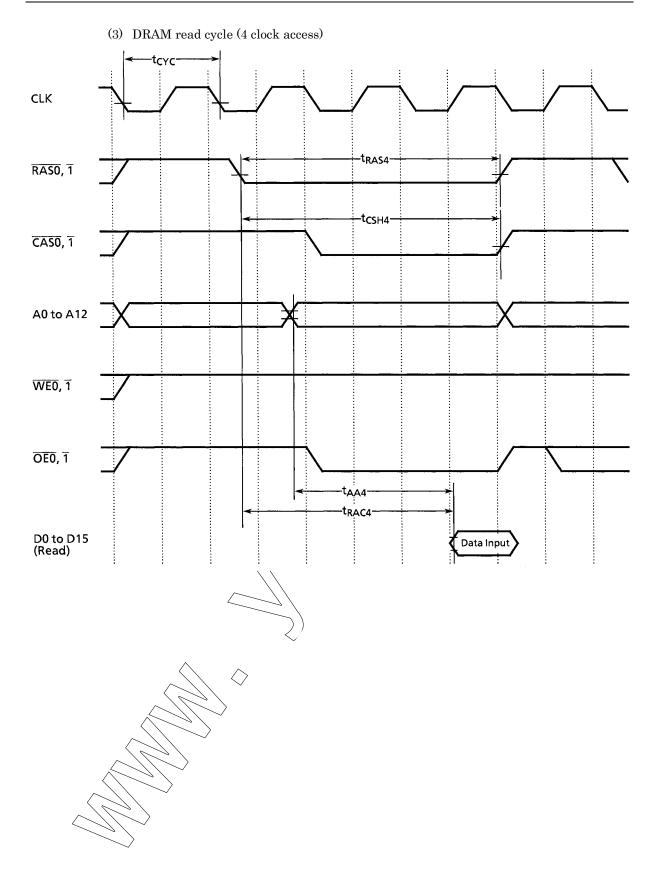

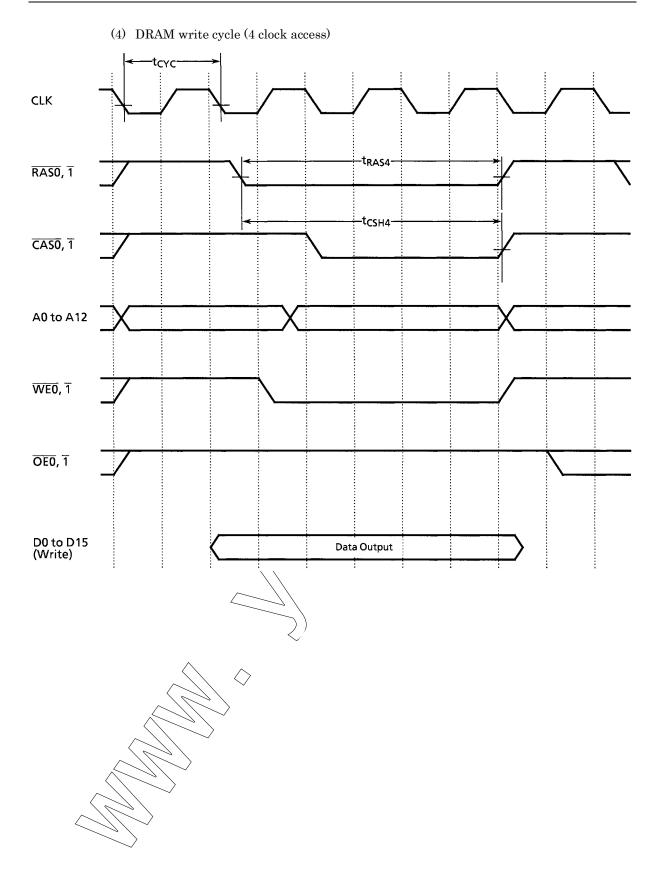

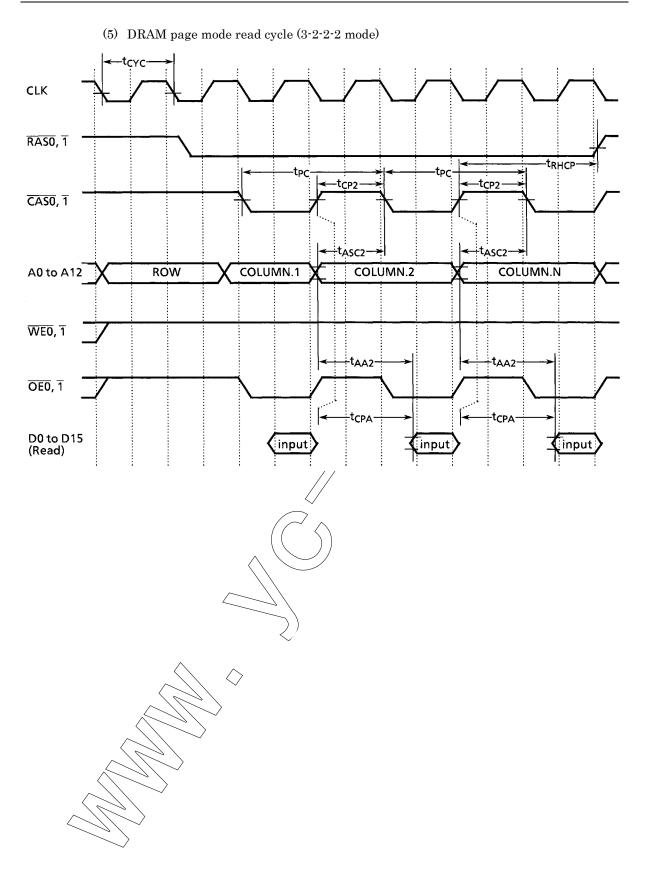

### 4.3.3 DRAM Bus Cycle

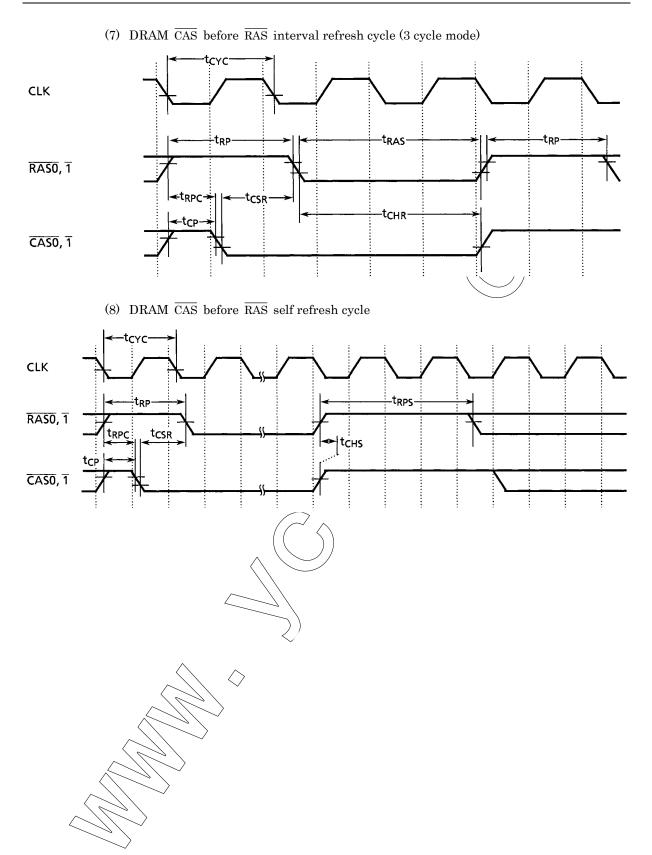

| No. | Symbol           | Parameter                                           | Min         | Max       | @20 MHz | @16 MHz | Unit |

|-----|------------------|-----------------------------------------------------|-------------|-----------|---------|---------|------|

| 34  | t <sub>DH</sub>  | Data Output Hold Time                               | 1.00×T-25   |           | 25      | 38      | ns   |

| 35  | t <sub>DHR</sub> | Data Output Hold Time from RAS                      | 1.75×T-5    |           | 83      | 104     | ns   |

| 36  | twcs             | Write Command Set-up Time                           | 0.50×T-20   |           | 5       | 11      | ns   |

| 37  | t <sub>CSR</sub> | CAS Set-up Time                                     | 0.75×T-20   |           | 18      | 27      | ns   |

| 38  | t <sub>CHR</sub> | CAS Hold Time                                       | 1.75×T-20   |           | 68      | 89      | ns   |

| 39  | t <sub>RPC</sub> | RAS Pre-charge CAS Active Time                      | 0.50 × T-20 |           | 5       | 11      | ns   |

| 40  | t <sub>ROH</sub> | RAS Hold Time from OE                               | 1.00 × T-20 |           | 30      | 43      | ns   |

| 41  | toea             | OE Access Time                                      |             | 1.00×T-40 | 10      | 23      | ns   |

| 42  | toez             | Input Data Hold Time from OE                        | 0           |           | 0       | 0       | ns   |

| 43  | t <sub>RPS</sub> | RAS Pre-charge Time<br>@ Release Self Refresh Cycle | 2.25×T-20   |           | 93      | 121     | ns   |

| 44  | t <sub>CHS</sub> | CAS Hold Time<br>@ Release Self Refresh Cycle       | - 15        |           | - 15    | - 15    | ns   |

AC Condition

Output: P0 to P1 (D0 to D15), P4 to P6 (A0 to A23), P70 (RD), P71 to R74 (WRx)

High = 2.0 V, Low = 0.8 V, CL = 50 pF

Others

High = 2.0 V, Low = 0.8 V, CL = 50 pF

Input: P0 to P1 (D0 to D15)

High = 2.4 V, Low = 0.45 V

Others

High = 0.8 Vcc, Low = 0.2 Vcc

### Event Counter (TI4, TI5, TI6, TI7, TI8, TI9, TIA, TIB) 4.4

| 1144 | ЛНz | 16 MHz |     | 20 MHz |     | Varia    | Parameter                    | Symbol            |

|------|-----|--------|-----|--------|-----|----------|------------------------------|-------------------|

| Unit | Max | Min    | Max | Min    | Max | Min      | Falanetei                    | Symbol            |

| ns   |     | 600    |     | 500    |     | 8T + 100 | Clock cycle                  | t <sub>VCK</sub>  |

| ns   |     | 290    |     | 240    |     | 4T + 40  | Clock low-level pulse width  | t <sub>VCKL</sub> |

| ns   |     | 290    |     | 240    |     | 4T + 40  | Clock high-level pulse width | t <sub>VCKH</sub> |

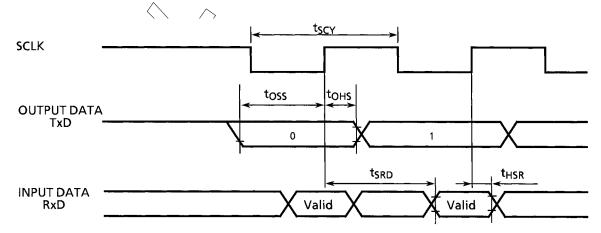

#### 4.5 Serial Channel Timing

(1) SCLK input mode (I/O interface mode)

| Symbol           | Parameter                                           | Variable                      |                             |     | ИHz | 16 MHz |     | Unit |  |

|------------------|-----------------------------------------------------|-------------------------------|-----------------------------|-----|-----|--------|-----|------|--|

| Symbol           |                                                     | Min                           | Max                         | Min | Max | Min    | Max | Unit |  |

| t <sub>SCY</sub> | SCLK cycle                                          | 16T                           |                             | 0.8 |     | 1.0    |     | μs   |  |

| t <sub>OSS</sub> | Output Data $\rightarrow$ Rising edge of SCLK       | t <sub>SCY</sub> /2 – 5T – 50 |                             | 100 |     | 138    |     | ns   |  |

| t <sub>ohs</sub> | SCLK rising edge $\rightarrow$ Output Data hold     | 5T – 100                      |                             | 150 |     | 213    |     | ns   |  |

| t <sub>HSR</sub> | SCLK rising edge $\rightarrow$ Input Data hold      | 0                             |                             | 0   |     | 0      |     | ns   |  |

| t <sub>SRD</sub> | SCLK rising edge $\rightarrow$ effective data input |                               | t <sub>SCY</sub> – 5T – 100 |     | 450 |        | 588 | ns   |  |

(2) SCLK output mode (I/O interface mode)  $Vcc = 5 V \pm 10\%$ , TA = -20 to 70°C (Internal 16 to 20 MHz)

| Symbol           | Parameter                                           | Varia                       | able                        | 20  | MHz   | 161 | ИНz | 11   |

|------------------|-----------------------------------------------------|-----------------------------|-----------------------------|-----|-------|-----|-----|------|

| Symbol           |                                                     | Min                         | Max                         | Min | Max   | Min | Max | Unit |

| t <sub>SCY</sub> | SCLK cycle (programmable)                           | 1 <b>6</b> T                | 8192T                       | 0.8 | 409.6 | 1.0 | 512 | μs   |

| t <sub>oss</sub> | Output Data $\rightarrow$ SCLK rising edge          | t <sub>SCY</sub> – 2T – 150 |                             | 550 |       | 725 |     | ns   |

| t <sub>OHS</sub> | SCLK rising edge $\rightarrow$ Output Data hold     | 2T – 80                     |                             | 20  |       | 45  |     | ns   |

| t <sub>HSR</sub> | SCLK rising edge $\rightarrow$ Input Data hold      | 0                           |                             | 0   |       | 0   |     | ns   |

| t <sub>SRD</sub> | SCLK rising edge $\rightarrow$ effective data input |                             | t <sub>SCY</sub> – 2T – 150 |     | 550   |     | 725 | ns   |

(3) SCLK input mode (UART mode)

′ Vcc = 5 V ± 10%, TA = − 20 to 70℃ (Internai 16 to 20 MHz)

| Symbol            | Parameter                   | Varia   | Variable |     | 20 MHz |     | 16 MHz |      |

|-------------------|-----------------------------|---------|----------|-----|--------|-----|--------|------|

| 5,                |                             | Min     | Max      | Min | Max    | Min | Max    | Unit |

| t <sub>SCY</sub>  | SCLK cycle                  | 4T + 20 |          | 220 |        | 270 |        | ns   |

| t <sub>SCYL</sub> | SCLK Low level Pulse width  | 2T + 5  |          | 105 |        | 130 |        | ns   |

| t <sub>SCYH</sub> | SCLK High level Pulse width | 2T + 5  |          | 105 |        | 130 |        | ns   |

#### 10-Bit AD Conversion Characteristics 4.6

|                                                           |                                                          | Vcc = 5 V ± 10         | 0%,TA = - 20 te | o 70℃ (Internal 16      | to 20 MHz |

|-----------------------------------------------------------|----------------------------------------------------------|------------------------|-----------------|-------------------------|-----------|

| Symbol                                                    | Parameter                                                | Min                    | Тур             | Max                     | Unit      |

| VREFH                                                     | Analog reference voltage (High)                          | V <sub>CC</sub> -0.2 V | Vcc             | Vcc                     | ·         |

| VREFL                                                     | Analog reference voltage (Low)                           | V <sub>SS</sub>        | Vss             | V <sub>SS</sub> + 0.2 V | v         |

| VAIN                                                      | Analog input voltage range                               | VREFL                  |                 | VREFH                   |           |

| IREF                                                      | Analog current for analog reference voltage              |                        |                 |                         |           |

| (VREFL = 0 V)                                             | $V_{CC} = 5V \pm 10\%$ <vrefon> = 1</vrefon>             |                        | 0.5             | 1.5                     | mA        |

|                                                           | $V_{CC} = 5V \pm 10\% \qquad \langle VREFON \rangle = 0$ |                        | 0.02            | 5.0                     | μA        |

| Error<br>(Quantize error<br>of ± 0.5 LSB not<br>included) | $V_{CC} = 5V \pm 10\%$ Total error                       |                        | ± 3.0           | ±6                      | LSB       |

Note 1:1LSB = (VREFH - VREFL)/1024 [V]

Note 2: Power supply current ICC from the digital power supply includes the power supply from the AVCC pin.

#### 8-Bit DA Conversion Characteristics 4.7

|             |                              |                                                   | = 5 K ± 10%,    | TA = -20 to 7 | 0°C (Internal 1       | 6 to 20 MHz) |

|-------------|------------------------------|---------------------------------------------------|-----------------|---------------|-----------------------|--------------|

| Symbol      | Parameter                    | Condition                                         | Min             | Тур           | Max                   | Unit         |

| DAREFH      | Analog reference voltage (+) |                                                   | 4.0             |               | V <sub>CC</sub>       | V            |

| DAREFL      | Analog reference voltage (-) |                                                   | V <sub>SS</sub> |               | V <sub>SS</sub>       | v            |

|             | Total error                  | RL = 2.4 KΩ                                       |                 | 2.0           | 4.0                   | LSB          |

|             | Output voltage range         | $RL = 2.4 \text{ K}\Omega$                        | $V_{SS} + 0.5$  |               | V <sub>SS</sub> – 0.5 | V            |

|             | Settling time                | $RL = 2.4 \text{ K}\Omega,$ $CL = 100 \text{ pF}$ |                 |               | 5                     | μS           |

| DAC         | Output impedance             |                                                   |                 |               | 5                     | Ω            |

| output mode | Resistive load               | $V_{SS} + 0.5 \le DAOUT \le V_{CC} - 0.5$         | 2.4             |               |                       | kΩ           |

Note: RL is the resistance load of the DA converter output in.

#### 4.8 Interrupt Operation

|                    |                                     | $Vcc = 5 V \pm 10\%$ , TA = - 20 to 70°C (internal 16 to 20 MHz) |     |        |     |        |     |      |  |

|--------------------|-------------------------------------|------------------------------------------------------------------|-----|--------|-----|--------|-----|------|--|

| Symbol             | Parameter                           | Variable                                                         |     | 20 MHz |     | 16 MHz |     |      |  |

|                    |                                     | Min                                                              | Max | Min    | Max | Min    | Max | Unit |  |

| t <sub>INTAL</sub> | NMI, INTO Low level Pulse width     | 4T                                                               |     | 200    |     | 250    |     | ns   |  |

| t <sub>INTAH</sub> | NMI, INTO High level Pulse width    | 4T                                                               |     | 200    |     | 250    |     | ns   |  |

| t <sub>INTBL</sub> | INT4 toINTB Low level Pulse width   | 8T + 100                                                         |     | 500    |     | 600    |     | ns   |  |

| t <sub>INTBH</sub> | INT4 to INTB High level Pulse width | 8T + 100                                                         |     | 500    |     | 600    |     | ns   |  |

|                  |                             | $Vcc = 5 V \pm 10\%$ , TA = $-20 \text{ to } 70 \degree$ (Internal 16 to 20 MHz) |            |     |        |     |        |      |  |

|------------------|-----------------------------|----------------------------------------------------------------------------------|------------|-----|--------|-----|--------|------|--|

| Symbol           | Parameter                   | V                                                                                | Variable   |     | 20 MHz |     | 16 MHz |      |  |

|                  |                             | Min                                                                              | Max        | Min | Max    | Min | Max    | Unit |  |

| t <sub>ABA</sub> | Floating time to BUSAK fall | 0                                                                                | <b>8</b> 0 | 0   | 80     | 0   | 80     | ns   |  |

| t <sub>BAA</sub> | Floating time to BUSAK rise | 0                                                                                | 80         | 0   | 80     | 0   | 80     | ns   |  |

Note: The bus will be released after the WAPT request is inactive, when the BUSRQ is set to "Low" during "wait" cycle.