- **Converts Light Intensity to Digital Signal**

- Infrared Compensation to Approximate Human Eye Response

- Companding A/D for Wide Dynamic Range

- **Rejects 50 Hz/60 Hz Lighting Ripple**

- **Two-Wire SMBus Serial Interface**

- Single Supply Operation (2.7 V to 5.5 V)

- Low Active Power (1 mW typ)

- **Power Down Mode**

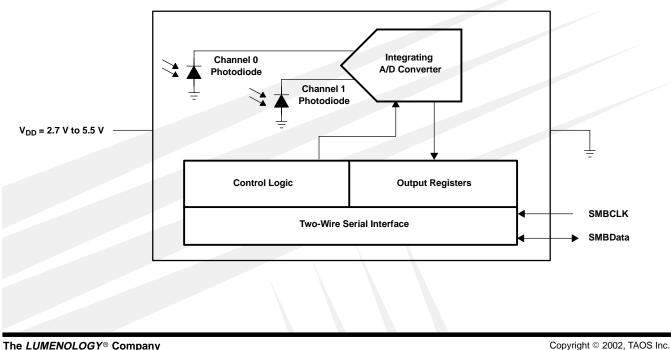

**Functional Block Diagram**

Low-Profile Surface-Mount Package

AMBIENT LIGHT SENSOR

TSL2550

#### Description

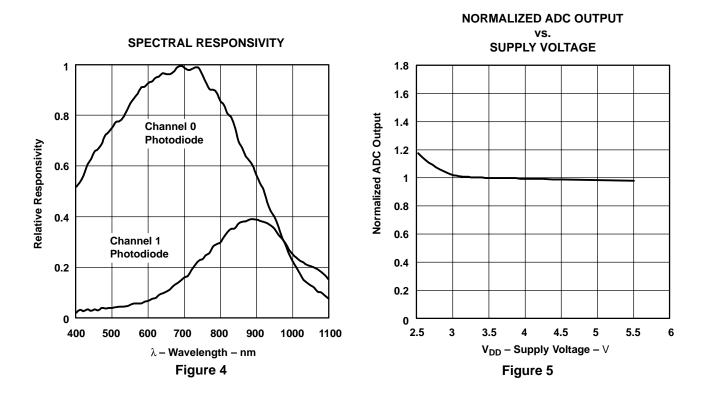

The TSL2550 is a digital light sensor with a two-wire, SMBus serial interface. It combines two photodiodes and a companding analog-to-digital converter (ADC) on a single CMOS integrated circuit to provide light measurements over an effective 12-bit dynamic range.

The TSL2550 is designed for use with broad wavelength light sources. One of the photodiodes (Channel 0) is sensitive to visible and infrared light, while the second photodiode (Channel 1) is sensitive primarily to infrared light. An integrating ADC converts the photodiode currents to Channel 0 and Channel 1 digital outputs. Channel 1 digital output is used to compensate for the effect of the infrared component of ambient light on Channel 0 digital output. The ADC digital outputs of the two channels are used to obtain a value that approximates the human eye response in the commonly used unit of Lux.

This device is intended primarily for use in applications in which measurement of ambient light is used to control display backlighting such as laptop computers, PDAs, camcorders, and GPS systems. Other applications include contrast control in LED signs and displays, camera exposure control, lighting controls, etc. The integrating conversion technique used by the TSL2550 effectively eliminates the effect of flicker from AC-powered lamps, increasing the stability of the measurement.

The LUMENOLOGY® Company

Texas Advanced Optoelectronic Solutions Inc. 800 Jupiter Road, Suite 205 • Plano, TX 75074 • (972) 673-0759

www.taosinc.com

# TSL2550 **AMBIENT LIGHT SENSOR** WITH SMBus INTERFACE

TAOS029 – SEPTEMBER 2002

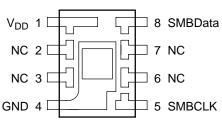

#### **Terminal Functions**

| TERMI           | TERMINAL |                                                                            |                                                            |  |  |  |

|-----------------|----------|----------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|

| NAME            | NO.      | TYPE                                                                       | DESCRIPTION                                                |  |  |  |

| GND             | 4        |                                                                            | Power supply ground. All voltages are referenced to GND.   |  |  |  |

| SMBCLK          | 5        | 5 I SMBus serial clock input terminal — clock signal for SMBus serial data |                                                            |  |  |  |

| SMBData         | 8        | I/O                                                                        | SMBus serial data I/O terminal — serial data I/O for SMBus |  |  |  |

| V <sub>DD</sub> | 1        |                                                                            | Supply voltage                                             |  |  |  |

#### **Available Options**

| DEVICE  | T <sub>A</sub>                 | PACKAGE – LEADS | PACKAGE DESIGNATOR | ORDERING NUMBER |

|---------|--------------------------------|-----------------|--------------------|-----------------|

| TSL2550 | $-25^{\circ}C$ to $85^{\circ}$ | SOIC-8          | D                  | TSL2550D        |

#### Absolute Maximum Ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>DD</sub> (see Note 1)         |                |

|------------------------------------------------------|----------------|

| Digital output voltage range, V <sub>O</sub>         |                |

| Digital output current, I <sub>O</sub>               | ±10 mA         |

| SMBus input/output current, I(SMBIN)                 | –1 mA to 20 mA |

| Operating free-air temperature range, T <sub>A</sub> | –25°C to 85°C  |

| Storage temperature range, T <sub>stg</sub>          | –25°C to 85°C  |

| ESD tolerance, human body model                      | 2000 V         |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are with respect to GND.

## **Recommended Operating Conditions**

|                                                                              | MIN | MAX | UNIT |

|------------------------------------------------------------------------------|-----|-----|------|

| Supply voltage, V <sub>DD</sub>                                              | 2.7 | 5.5 | V    |

| Operating free-air temperature, T <sub>A</sub>                               | 0   | 70  | °C   |

| SMBus input low voltage @ $V_{DD}$ = 3.3 V ± 5%, V <sub>IL</sub>             |     | 0.8 | V    |

| SMBus input high voltage @ V <sub>DD</sub> = 3.3 V $\pm$ 5%, V <sub>IH</sub> | 2.1 |     | V    |

| SMBus operating frequency, f <sub>(SMBCLK)</sub>                             | 10  | 100 | kHz  |

# TSL2550 AMBIENT LIGHT SENSOR WITH SMBus INTERFAC

TAOS029 - SEPTEMBER 2002

#### Electrical Characteristics over recommended operating free-air temperature range (unless otherwise noted)

|                 | PARAMETER                  | TEST CONDITIONS                                                                  | MIN | TYP  | MAX | UNIT |

|-----------------|----------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| v               | SMDue eutruit leur voltege | I <sub>O</sub> = 50 μA                                                           |     | 0.01 |     | V    |

| V <sub>OL</sub> | SMBus output low voltage   | $I_{O} = 4 \text{ mA}$                                                           |     |      | 0.4 | V    |

|                 | Querely contract           | Active, VSMBCLK and VSMDATA = V <sub>DD</sub> , V <sub>DD</sub> = 3.3 V $\pm$ 5% |     | 0.35 | 0.6 | mA   |

| IDD             | Supply current             | Power down, VSMBCLK and VSMDATA = $V_{DD,}V_{DD}$ = 3.3 V $\pm$ 5%               |     |      | 10  | μΑ   |

| I <sub>IH</sub> | High level input current   | VI = V <sub>DD</sub>                                                             |     |      | 5   | μA   |

| IIL             | Low level input current    | VI = 0                                                                           |     |      | -5  | μA   |

# Operating Characteristics, V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = 25°C (unless otherwise noted) (see Notes 2, 3, 4)

|                | PARAMETER                            | TEST CONDITIONS                                                    | CHANNEL | MIN   | TYP   | MAX   | UNIT                                 |

|----------------|--------------------------------------|--------------------------------------------------------------------|---------|-------|-------|-------|--------------------------------------|

|                |                                      | <b>F</b> 0                                                         | Ch0     |       |       | 1     |                                      |

|                |                                      | $E_e = 0$                                                          | Ch1     |       |       | 1     |                                      |

|                |                                      | λ <sub>p</sub> = 640 nm                                            | Ch0     | 639   | 799   | 959   |                                      |

|                | ADC count value                      | $\dot{E}_{e} = 81 \mu\text{W/cm}^2$                                | Ch1     |       | 85    |       | counts                               |

|                |                                      | λ <sub>p</sub> = 940 nm                                            | Ch0     | 511   | 799   | 1039  |                                      |

|                |                                      | $E_{e} = 172 \mu\text{W/cm}^2$                                     | Ch1     |       | 703   |       |                                      |

|                |                                      | $\lambda_p = 640 \text{ nm}, \text{ E}_e = 81 \ \mu\text{W/cm}^2$  |         | 0.075 | 0.106 | 0.175 |                                      |

|                | ADC count value ratio: Ch1/Ch0       | $\lambda_p = 940 \text{ nm}, \text{ E}_e = 172 \ \mu\text{W/cm}^2$ |         | 0.75  | 0.88  | 1.05  |                                      |

|                |                                      | λ <sub>p</sub> = 640 nm                                            | Ch0     |       | 9.9   |       | counts/<br>(μW/<br>cm <sup>2</sup> ) |

|                | tion d'anna anns an Arthur           | $\dot{E}_{e} = 81 \mu\text{W/cm}^2$                                | Ch1     |       | 1     |       |                                      |

| R <sub>e</sub> | Irradiance responsivity              | λ <sub>p</sub> = 940 nm                                            | Ch0     |       | 4.6   |       |                                      |

|                |                                      | $\dot{E}_{e} = 172 \mu\text{W/cm}^2$                               | Ch1     |       | 4.1   |       |                                      |

|                |                                      | Element l'altra anno 200 lan                                       | Ch0     |       | 2.8   |       |                                      |

|                |                                      | Fluorescent light source: 300 Lux                                  | Ch1     |       | 0.23  |       | counts/<br>lux                       |

| Rv             | Illuminance responsivity             |                                                                    | Ch0     |       | 19    |       |                                      |

|                |                                      | Incandescent light source: 50 Lux                                  | Ch1     |       | 13    |       |                                      |

|                |                                      | Fluorescent light source: 300 Lux                                  |         | 0.65  | 1     | 1.35  |                                      |

|                | (Sensor Lux) / (actual Lux) (Note 5) | Incandescent light source: 50 Lux                                  |         | 0.5   | 1     | 1.5   |                                      |

NOTES: 2. Optical measurements are made using small-angle incident radiation from light-emitting diode optical sources. Visible 640 nm LEDs and infrared 940 nm LEDs are used for final product testing for compatibility with high volume production.

3. The 640 nm irradiance Ee is supplied by an AIInGaP light-emitting diode with the following characteristics: peak wavelength  $\lambda p$  = 640 nm and spectral halfwidth  $\Delta \lambda^{1/2}$  = 17 nm.

4. The 940 nm irradiance Ee is supplied by a GaAs light-emitting diode with the following characteristics: peak wavelength  $\lambda p = 940$  nm and spectral halfwidth  $\Delta \lambda^{1/2} = 40$  nm.

5. The sensor Lux is calculated using the empirical formula shown on p. 12 of this data sheet based on measured Ch0 and Ch1 ADC count values for the light source specified. Actual Lux is obtained with a commercial luxmeter. The range of the (sensor Lux) / (actual Lux) ratio is estimated based on the variation of the 640 nm and 940 nm optical parameters. Devices are not 100% tested with fluorescent or incandescent light sources.

# TSL2550 AMBIENT LIGHT SENSOR WITH SMBus INTERFACE

TAOS029 – SEPTEMBER 2002

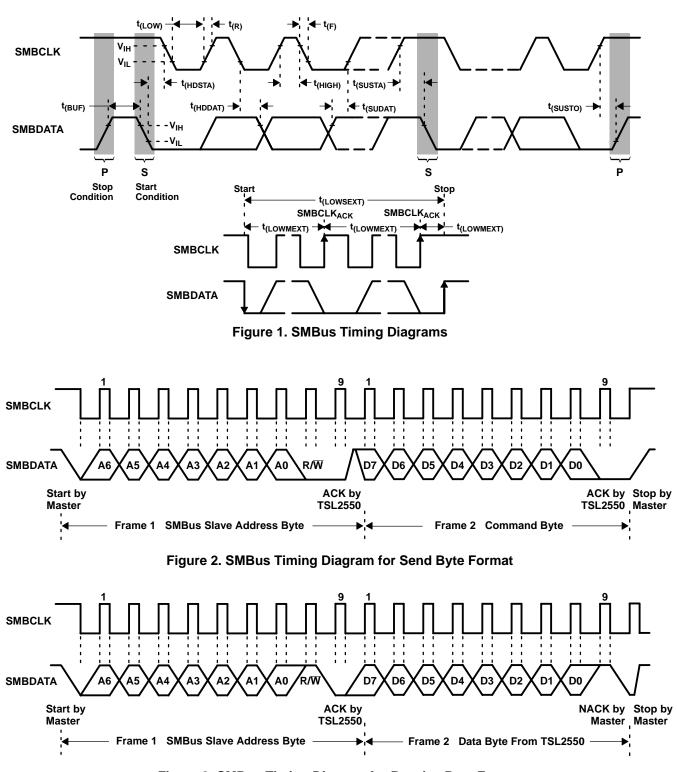

# AC Electrical Characteristics, $V_{DD}$ = 3.3 V, $T_{A}$ = 25°C (unless otherwise noted)

|                        | PARAMETER                                                                                    | TEST CONDITIONS | MIN | TYP | MAX  | UNIT |

|------------------------|----------------------------------------------------------------------------------------------|-----------------|-----|-----|------|------|

| t <sub>(CONV)</sub>    | Conversion time, per channel                                                                 |                 |     | 400 |      | ms   |

| f(SMBCLK)              | Clock frequency                                                                              |                 |     |     | 100  | kHz  |

| t <sub>(BUF)</sub>     | Bus free time between start and stop condition                                               |                 | 4.7 |     |      | μs   |

| t(HDSTA)               | Hold time after (repeated) start condition. After this period, the first clock is generated. |                 | 4   |     |      | μs   |

| t <sub>(SUSTA)</sub>   | Repeated start condition setup time                                                          |                 | 4.7 |     |      | μs   |

| t <sub>(SUSTO)</sub>   | Stop condition setup time                                                                    |                 | 4   |     |      | μs   |

| t <sub>(HDDAT)</sub>   | Data hold time                                                                               |                 | 300 |     |      | ns   |

| t <sub>(SUDAT)</sub>   | Data setup time                                                                              |                 | 250 |     |      | ns   |

| t <sub>(LOW)</sub>     | SMBCLK clock low period                                                                      |                 | 4.7 |     |      | μs   |

| t <sub>(HIGH)</sub>    | SMBCLK clock high period                                                                     |                 | 4   |     |      | μs   |

| t <sub>(TIMEOUT)</sub> | Detect clock/data low timeout                                                                |                 | 25  |     | 35   | ms   |

| t <sub>F</sub>         | Clock/data fall time                                                                         |                 |     |     | 300  | ns   |

| t <sub>R</sub>         | Clock/data rise time                                                                         |                 |     |     | 1000 | ns   |

| Ci                     | Input pin capacitance                                                                        |                 |     |     | 10   | pF   |

Copyright © 2002, TAOS Inc.

The LUMENOLOGY® Company

PARAMETER MEASUREMENT INFORMATION

Figure 3. SMBus Timing Diagram for Receive Byte Format

## **TYPICAL CHARACTERISTICS**

## PRINCIPLES OF OPERATION

#### Analog-to-Digital Converter

The TSL2550 contains an integrating analog-to-digital converter (ADC) that integrates a photodiode current. First it integrates channel 0 photodiode current and then it integrates channel 1 photodiode current. At the end of the conversion cycle for each channel (approximately 400 ms), the conversion result is transferred to the appropriate channel 0 or channel 1 ADC register. The transfer is double-buffered to ensure that invalid data is not read during the transfer. After the data is transferred, the TSL2550 automatically begins the next conversion cycle. Approximately 800 ms is required for both Channel 0 and Channel 1 ADC registers to be updated. A VALID bit is used to indicate that data has been written to the ADC register after ADC is enabled.

Interface to the ADC and control of other device functions is accomplished using the standard 2-wire System Management Bus (SMBus) interface. Both versions 1.1 and 2.0 of the SMBus are supported.

#### **Digital Interface**

The TSL2550 contains an 8-bit command register that can be written and read via the SMBus. The command register controls the overall operation of the device. There are two read-only registers that contain the latest converted value of each of the two ADC channels. The SMBus slave address is hardwired internally as 0111001 (MSB to LSB, A6 to A0).

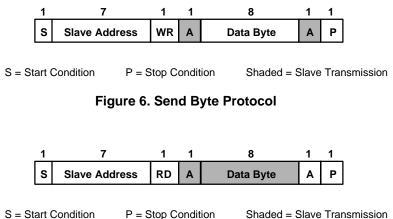

Both the send byte protocol and the receive byte protocol are implemented in the TSL2550. The send byte protocol allows single bytes of data to be written to the device (see Figure 6). The written byte is called the COMMAND byte. The receive byte protocol allows single bytes of data to be read from the device (see Figure 7). The receive data can be either the previously written COMMAND byte or the data from one of the ADC channels.

P = Stop Condition Shaded = Slave Transmission

Figure 7. Receive Byte Protocol

#### TSL2550 AMBIENT LIGHT SENSOR WITH SMBus INTERFACE TAOS029 – SEPTEMBER 2002

#### **Command Register**

The command register contains eight bits as described in Table 1 and defaults to 0 (0x00) at power-up. A command summary appears in Table 2.

| RSEL  |       |       |    | RESERVED | ADCEN | PON   |     |

|-------|-------|-------|----|----------|-------|-------|-----|

| B7    | B6    | B5    | B4 | B3       | B2    | B1    | B0  |

| RSEL2 | RSEL1 | RSEL0 | 0  | 0        | 0     | ADCEN | PON |

Table 1. Command Register Data Format

| FIELD                                                                                                                                                          | BITS   |                                                                                     | DESCRIPTION                                                                                                                                                                                                                         |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| RSEL                                                                                                                                                           | 7 to 5 | Read Data Select. This field determines the data output by the TSL2550 Juring read. |                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                |        | Field Value                                                                         | Read Value                                                                                                                                                                                                                          |  |  |  |  |

|                                                                                                                                                                |        | 000                                                                                 | Command register                                                                                                                                                                                                                    |  |  |  |  |

|                                                                                                                                                                |        | 010                                                                                 | ADC channel 0                                                                                                                                                                                                                       |  |  |  |  |

|                                                                                                                                                                |        | 100                                                                                 | ADC channel 1                                                                                                                                                                                                                       |  |  |  |  |

| RESERVED                                                                                                                                                       | 4 to 2 | Reserved for factory test                                                           | eserved for factory test. These bits should always be written to 0.                                                                                                                                                                 |  |  |  |  |

| ADCEN                                                                                                                                                          | 1      | ADC Enable. This field a Writing a 0 disables the PON.                              | actives the ADC. Writing a 1 activates the ADC.<br>ADC. ADCEN is normally used in conjunction with                                                                                                                                  |  |  |  |  |

|                                                                                                                                                                |        | <i>Note:</i> Both ADCEN and operate correctly.                                      | PON must be asserted before the ADC channels will                                                                                                                                                                                   |  |  |  |  |

|                                                                                                                                                                |        | ADC channels to operate                                                             | Power ON. This field activates the internal oscillator to permit the timers and ADC channels to operate. Writing a 1 activates the oscillator. Writing a 0 disables the oscillator. PON is normally used in conjunction with ADCEN. |  |  |  |  |

| PON 0 <b>Note:</b> For the Duration of writes and reads over the SMB interface, this overridden and the oscillator is enabled, independent of the state of POI |        |                                                                                     |                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                                                                                                                |        | <i>Note:</i> Both ADCEN and operate correctly.                                      | PON must be asserted before the ADC channels will                                                                                                                                                                                   |  |  |  |  |

The command register is used primarily to select which register will be read during a read cycle (RSEL) and to control the power consumption of the device (ADCEN and PON). When ADCEN and PON are high, the device is in the full powered-up state and is fully operational. When ADCEN and PON are low, both the ADC and the internal oscillator are powered down, resulting in minimum power consumption. *Both ADCEN and PON should always be asserted and de-asserted together.* The remaining bits (B4, B3, and B2) in the command register should always be written 0. For details on using the command register, see the *Operation* section, below.

| COMMAND | FUNCTION                         |

|---------|----------------------------------|

| 00h     | Place device in power-down state |

| 03h     | Read command register            |

| 43h     | Read ADC Channel 0               |

| 83h     | Read ADC Channel 1               |

#### **ADC Register**

The TSL2550 contains two ADC registers (channel 0 and channel 1). Each ADC register contains two components to determine the logarithmic ADC count value: CHORD bits and STEP bits. The CHORD bits correspond to the most significant portion of the ADC value and specifies a segment of the piece-wise linear approximation. The STEP bits correspond to the least significant portion of the ADC count value and specifies a linear value within a segment. CHORD and STEP bits all equal to 0 corresponds to a condition in which the light level is below the detection limit of the sensor. CHORD and STEP bits all equal to 1 corresponds to an overflow condition.

Each of the two ADC value registers contain seven bits as described in Table 3. The specific ADC value register read depends on the last written RSEL field to the command register, as described above and in the *Operation* section, below.

| VALID | VALID CHORD BITS |    |    |    | STEP BITS |    |    |  |

|-------|------------------|----|----|----|-----------|----|----|--|

| B7    | B6               | B5 | B4 | B3 | B2        | B1 | B0 |  |

| VALID | C2               | C1 | C0 | S3 | S2        | S1 | S0 |  |

| FIELD | BITS   | DESCRIPTION                                                                                                                                              |

|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| VALID | 7      | ADC channel data is valid. One indicates that the ADC has written data into the channel data register, since ADCEN was asserted in the COMMAND register. |

| CHORD | 6 to 4 | CHORD number.                                                                                                                                            |

| STEP  | 3 to 0 | STEP number.                                                                                                                                             |

The MSB of the ADC register (VALID bit B7) is used to indicate that data has been written to the ADC register after the ADC and internal oscillator are activated as described in *Command Register* section.

Bits 6 through 0 contain the 7-bit code representing the ADC count value, which is proportional to a photodetector current. In this code, the ADC count value is represented by a piece-wise linear approximation to a log function. The transfer function is broken into 8 chords of 16 steps each. (This code is very similar to  $\mu$ -law code used in audio compression — it differs in that it does not have a sign bit and it is not inverted.) Table 4 shows the relationship between the CHORD and STEP bits and the CHORD and STEP numbers and values. These are used to calculate the ADC count value.

# TSL2550 **AMBIENT LIGHT SENSOR** WITH SMBus INTERFACE

| CHORD<br>BITS<br>B6, B5, B4 | C, CHORD<br>NUMBER | CHORD<br>VALUE<br>(Note A) | STEP<br>VALUE<br>(Note B) |

|-----------------------------|--------------------|----------------------------|---------------------------|

| 000                         | 0                  | 0                          | 1                         |

| 001                         | 1                  | 16                         | 2                         |

| 010                         | 2                  | 49                         | 4                         |

| 011                         | 3                  | 115                        | 8                         |

| 100                         | 4                  | 247                        | 16                        |

| 101                         | 5                  | 511                        | 32                        |

| 110                         | 6                  | 1039                       | 64                        |

| 111                         | 7                  | 2095                       | 128                       |

| Table 4. CHORD and ST | P Numbers and | Values vs R | Register Bits |

|-----------------------|---------------|-------------|---------------|

|-----------------------|---------------|-------------|---------------|

| STEP<br>BITS<br>B3, B2, B1, B0 | S, STEP<br>NUMBER |  |

|--------------------------------|-------------------|--|

| 0000                           | 0                 |  |

| 0001                           | 1                 |  |

| 0010                           | 2                 |  |

| 0011                           | 3                 |  |

| 0100                           | 4                 |  |

| 0101                           | 5                 |  |

| 0110                           | 6                 |  |

| 0111                           | 7                 |  |

| 1000                           | 8                 |  |

| 1001                           | 9                 |  |

| 1010                           | 10                |  |

| 1011                           | 11                |  |

| 1100                           | 12                |  |

| 1101                           | 13                |  |

| 1110                           | 14                |  |

| 1111                           | 15                |  |

NOTES: A. CHORD VALUE = INT  $(16.5 \times ((2^{C}) - 1))$ B. STEP VALUE =  $2^{C}$

> The ADC count value is obtained by adding the CHORD VALUE and the product of the STEP NUMBER and STEP VALUE (which depends on CHORD NUMBER).

> > ADC Count Value = ((Chord Value) + (Step Size) × (Number of Steps))

The ADC count value is as a formula:

ADC Count Value = (INT  $(16.5 \times ((2^{c} - 1))) + (S \times (2^{c}))$

where:

С is the CHORD NUMBER (0 to 7) is the STEP NUMBER (0 to 15) S as defined in Table 4.

#### Operation

After applying VDD, the device will initially be in the power down state. To operate the device, issue an SMBus Send Byte protocol with the device address and the appropriate command byte to read ADC channel 0 or ADC channel 1 (see Table 2). To obtain the conversion result, issue an SMBus Receive Byte protocol with the device address. The data byte received will correspond to the value in the ADC register (0 or 1) specified by the previous command. If a conversion has not been completed since power up (either through  $V_{DD}$  or ADCEN/PON), the valid bit will be 0, and the data will not be valid. If there is a valid conversion result available, the valid bit will be set (1), and the remaining 7 bits will represent valid data from the previously selected ADC register. Data may be read repeatedly from the currently selected ADC register, and although it will remain valid, the ADC register will not be updated until a new conversion completes for that channel (800 ms total since there are two serial 400 ms per channel conversion times). Note also that the command register itself may be read, as a check to be sure that the device is communicating properly.

To power down the device for reduced power consumption, issue an SMBus Send Byte protocol with the device address followed by 0 to clear the ADCEN and PON bits.

## **APPLICATION INFORMATION**

The TSL2550 is intended for use in ambient light detection applications, such as display backlight control, where adjustments are made to display brightness or contrast based on the brightness of the ambient light, as perceived by the human eye. Conventional silicon detectors respond strongly to infrared light, which the human eye does not see. This can lead to significant error when the infrared content of the ambient light is high, such as with incandescent lighting, due to the difference between the silicon detector response and the brightness perceived by the human eye.

This problem is overcome in the TSL2550 through the use of two photodiodes. One of the photodiodes (Channel 0) is sensitive to both visible and infrared light, while the second photodiode (Channel 1) is sensitive primarily to infrared light. An integrating ADC converts the photodiode currents to Channel 0 and Channel 1 digital outputs. Channel 1 digital output is used to compensate for the effect of the infrared component of light on the Channel 0 digital output. The ADC digital outputs from the two channels are used in a formula to obtain a value that approximates the human eye response in the commonly used Illuminance unit of Lux:

where:

Light Level (lux) = (Ch0 Counts)  $\times$  (0.46)  $\times$  (e<sup>(-3.13R)</sup>)

R = (Ch1 Counts) / (Ch0 Counts)

The formula above was obtained by optical testing with fluorescent and incandescent light sources. The light level calculated from the formula will be slightly higher than the actual light level for sunlight and will be slightly lower than the actual light level for composite fluorescent and incandescent light sources.

Table 5 contains a summary of the typical sensor outputs for several common light sources.

| LIGHT SOURCE     | ILLUMINANCE<br>(LUX) | CHANNEL 0<br>(COUNTS) | CHANNEL 1<br>(COUNTS) | RATIO:<br>CH1/CH0 | LUX per CH0<br>COUNT |

|------------------|----------------------|-----------------------|-----------------------|-------------------|----------------------|

| Fluorescent      | 300                  | 831                   | 68                    | 0.082             | 0.36                 |

| Daylight (shade) | 100                  | 895                   | 343                   | 0.38              | 0.11                 |

| Incandescent     | 50                   | 959                   | 671                   | 0.7               | 0.052                |

#### Table 5. Sensor Output Summary

Light from 50 or 60 Hz sources, and especially fluorescent lighting, has a high harmonic content. Since the TSL2550 integrates the ambient light over an approximately 400 millisecond interval (per channel), this light ripple is typically reduced to less than 1/4 LSB.

## **Power Supply Decoupling**

The power supply lines must be decoupled with a 0.1  $\mu$ F capacitor placed as close to the device package as possible. The bypass capacitor should have low effective series resistance (ESR) and effective series inductance (ESI), such as the common ceramic types, which provide a low impedance path to ground at high frequencies to handle transient currents caused by internal logic switching.

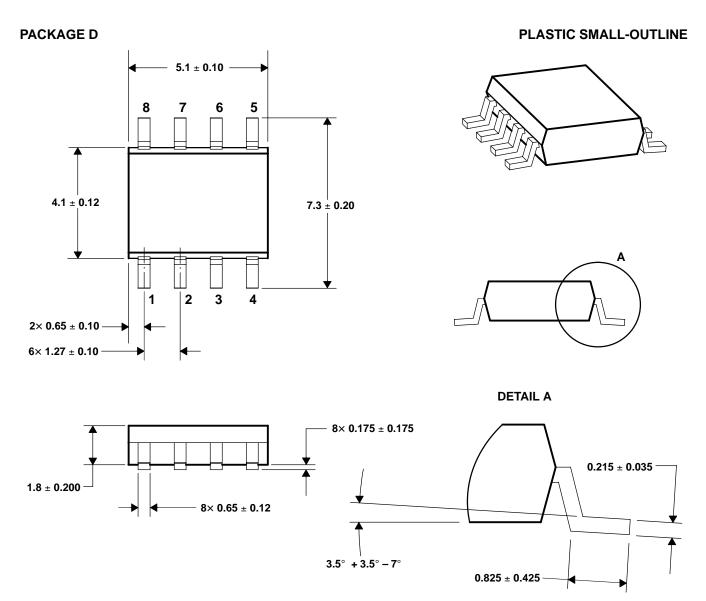

## **MECHANICAL DATA**

#### NOTES: A. All linear dimensions are in millimeters.

The LUMENOLOGY® Company

- B. Package is molded with an electrically nonconductive clear plastic compound having an index of refraction of 1.55.

- C. Actual product will vary within the mechanical tolerances shown on this specification. Designs for use of this product MUST allow for the data sheet tolerances.

- D. This drawing is subject to change without notice.

**PRODUCTION DATA** — information in this document is current at publication date. Products conform to specifications in accordance with the terms of Texas Advanced Optoelectronic Solutions, Inc. standard warranty. Production processing does not necessarily include testing of all parameters.

# NOTICE

Texas Advanced Optoelectronic Solutions, Inc. (TAOS) reserves the right to make changes to the products contained in this document to improve performance or for any other purpose, or to discontinue them without notice. Customers are advised to contact TAOS to obtain the latest product information before placing orders or designing TAOS products into systems.

TAOS assumes no responsibility for the use of any products or circuits described in this document or customer product design, conveys no license, either expressed or implied, under any patent or other right, and makes no representation that the circuits are free of patent infringement. TAOS further makes no claim as to the suitability of its products for any particular purpose, nor does TAOS assume any liability arising out of the use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

TEXAS ADVANCED OPTOELECTRONIC SOLUTIONS, INC. PRODUCTS ARE NOT DESIGNED OR INTENDED FOR USE IN CRITICAL APPLICATIONS IN WHICH THE FAILURE OR MALFUNCTION OF THE TAOS PRODUCT MAY RESULT IN PERSONAL INJURY OR DEATH. USE OF TAOS PRODUCTS IN LIFE SUPPORT SYSTEMS IS EXPRESSLY UNAUTHORIZED AND ANY SUCH USE BY A CUSTOMER IS COMPLETELY AT THE CUSTOMER'S RISK.

LUMENOLOGY is a registered trademark, and TAOS, the TAOS logo, and Texas Advanced Optoelectronic Solutions are trademarks of Texas Advanced Optoelectronic Solutions Incorporated.