# **WAN-0149**

## Pin Compatibility of the WM8766/68/72

#### INTRODUCTION

The WM8766/68/72 is a family of six and eight channel DACs and one Codec. They are designed to be pin compatible in most applications and share identical register structures. This document demonstrates how easily interchangeable the devices are.

#### **PIN OUT OF THE WM8766/68/72**

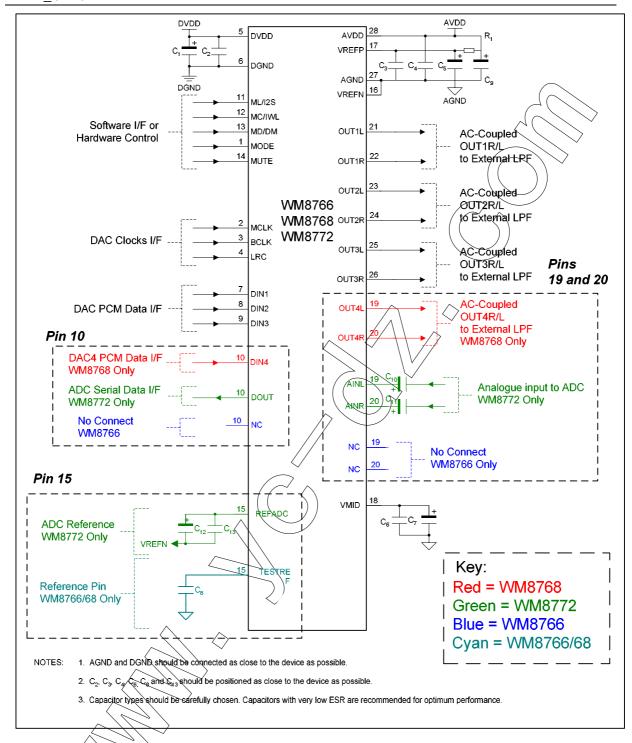

Figure 1 below shows the pin-out of all devices.

- WM8766: Fourth pair of outputs (pins 19 and 20) and the fourth digital input (pin 10) are missing from the device leaving No Connection pins instead.

- WM8768: Four sets of stereo outputs can be seen down the right hand side of the device with the digital inputs on the left hand side.

- WM8772: Pins 19,20,10 are used as analogue inputs and a digital output for the ADC.

#### WM8766, PIN CONFIGURATION 28 WM8768, PIN CONFIGURATION WM8772, PIN CONFIGURATION 28 **LEAD SSOP** 28 LEAD SSOP LEAD SSOP 28 27 26 25 28 AVDD 28 AVDD MODE ☐ 1 ● MODE AVDD MODE ☐ 1 ● MCLK 🔲 2 27 AGND MCLK AGND MCLK 2 27 AGND BCLK 3 26 □ VOUT3R BCLK 🔲 3 26 ☐ VOUT3R BCLK 3 VOUTOR 25 VOUT3L 25 VOUT3L LRCLK 4 LRCLK ☐ 4 VOUT3Ľ LRC 4 DVDD 5 24 □ VOUT2R 24 23 DVDD 5 24 DVDD VOUT2R 23 VOUT2L DGND -DGND 6 23 VOUT2L VOUT2L DIN1 7 DIN2 8 VOUT1R DIN1 7 DIN1 22 21 22 VOUT1R VOUT1R DIN2 | 8 21 VOUT1L DIN2 VOUT1L DIN3 9 DNC 10 20 ☐ NC DIN3 🔲 9 20 AINL 20 VOUT4R 19 □ NC 19 VOUT4L DOUT [ 10 19 AINR 18 VMID 18 18 VMID ML/I2S VMID WD/DM WC/IMF 17 VREFP 17 17 VREFP VREFP 12 MD/DM | 13 16 VREFN VREFN MD/DM 🗍 13 16 VREFN 13 MUTE TESTREF 15 TESTREF MUTE 🔲 14 15 REFADC

Figure 1 WM8766, WM8768 WM8772 Pin Configurations

The stereo channel VOUT4L/R has the same properties as the other three stereo channels (i.e. VOUT1L/R, VOUT3L/R) for the WM8768 device. The analogue inputs to the WM8772 should be connected via AC coupling capacitors.

Figure 2 overleaf shows the recommended external components for all 3 devices. Common pins are shown in black, pins that vary from device to device are colour coded.

Figure 2 WM8766/68/72 Recommended External Components Diagram

| COMPONENT<br>REFERENCE | SUGGESTED<br>VALUE | DESCRIPTION                                                |

|------------------------|--------------------|------------------------------------------------------------|

| C1 and C5              | 10μF               | De-coupling for DVDD and AVDD.                             |

| C2 to C4               | 0.1μF              | De-coupling for DVDD and AVDD.                             |

| C6                     | 0.1μF              | Reference de-coupling capacitors for VMID and TESTREF pin. |

| C7                     | 10μF               |                                                            |

| C8                     | 0.1μF              | De-coupling for TESTREF.                                   |

| C9                     | 10μF               | Filtering for VREFP. Omit if AVDD low noise.               |

| C10                    | 1μF                | AC coupling for analogue input                             |

| C11                    | 1μF                | AC coupling for analogue input                             |

| C12                    | 10μF               | De-coupling for ADC ref                                    |

| C13                    | 0.1μF              | De-coupling for ADC ref                                    |

| R1                     | 33Ω                | Filtering for VREP. Use $0\Omega$ if AVDD low noise.       |

**Table 1 External Components Description**

#### **REGISTER MAPS OF THE WM8766/68/72**

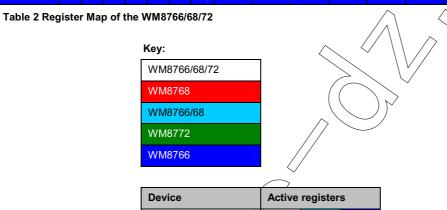

The register maps of the WM8766/68/72 are shown below in Table 2. Register R0-R9 and R31 are common to all devices with additional registers for VOVT4 in the WM8768 and the ADC in the WM8772.

The table shows all registers for all devices. The keys below this describe which rows represent each device. For example, row R15(0Fh) describes register R15 for the WM8766 and row R15(0Fh) describes R15 in the WM8768. Registers in white rows are common to all devices.

| REGISTER | B<br>1<br>5 | B<br>1<br>4 | B<br>1<br>3 | B<br>1<br>2 | B<br>1<br>1 | B<br>1<br>0 | B<br>9 | В8                                  | В7                     | В6   | B5 | B4  | В3  | B2              | B1               | В0              | DEFAULT   |

|----------|-------------|-------------|-------------|-------------|-------------|-------------|--------|-------------------------------------|------------------------|------|----|-----|-----|-----------------|------------------|-----------------|-----------|

| R0(00h)  | 0           | 0           | 0           | 0           | 0           | 0           | 0      | UPDATE                              | DATE LDA1[7:0]         |      |    |     |     |                 |                  | 011111111       |           |

| R1(01h)  | 0           | 0           | 0           | 0           | 0           | 0           | 1      | UPDATE                              | JPDATE RDA1[7:0]       |      |    |     |     |                 |                  | 011111111       |           |

| R2(02h)  | 0           | 0           | 0           | 0           | 0           | 1           | 0      |                                     | PLI                    | 8:5] |    | IZD | ATC | PDWN<br>All DAC | DEEMP<br>ALL DAC | MUTE<br>All DAC | 100100000 |

| R3(03h)  | 0           | 0           | 0           | 0           | 0           | 1           | 1      | F                                   | PHASE[8:6] DACIWL[5:4] |      |    |     |     | DACLRP          | DACFI            | MT[1:0]         | 000000000 |

| R4(04h)  | 0           | 0           | 0           | 0           | 1           | 0           | 0      | <b>V</b> PDATE                      | PPDATE LDA2[7:0]       |      |    |     |     |                 |                  | 011111111       |           |

| R5(05h)  | 0           | 0           | 0           | 0           | 1           | 0           | 1      | UPDATE                              | UPDATE RDA2[7:0]       |      |    |     |     |                 |                  | 011111111       |           |

| R6(06h)  | 0           | 0           | 0           | 0           | 1           | 1           | 0      | UPDATE                              | UPDATE LDA3[7:0]       |      |    |     |     |                 |                  | 011111111       |           |

| R7(07h)  | 0           | 0           | 0           | 0           | 1           | 1           | 1      | UPDATE RDA3[7:0]                    |                        |      |    |     |     |                 | 011111111        |                 |           |

| R8(08h)  | 0           | 0           | 0           | 1           | 0           | 0           | 0      | UPDATE                              | UPDATE MASTDA[7:0]     |      |    |     |     |                 |                  | 011111111       |           |

| R9(09h)  | 0           | 0           | 0           | 1           | 0           | 0           | 1      | DEEMP[8:6] DMUTE[5:3] DZFM[2:1] ZCD |                        |      |    |     |     | ZCD             | 000000000        |                 |           |

| R31(1Fh) | 0           | 0           | 1           | 1           | 1           | 1           | 1      | RESET                               |                        |      |    |     |     |                 | 000000000        |                 |           |

## WAN\_0149

| REGISTER | B<br>1<br>5 | B<br>1<br>4 | B<br>1<br>3 | B<br>1<br>2 | B<br>1<br>1 | B<br>1<br>0 | B<br>9 | В8         | В7           | В6        | B5    | B4           | В3             | B2           | B1     | В0     | DEFAULT   |  |

|----------|-------------|-------------|-------------|-------------|-------------|-------------|--------|------------|--------------|-----------|-------|--------------|----------------|--------------|--------|--------|-----------|--|

| R10(0Ah) | 0           | 0           | 0           | 1           | 0           | 1           | 0      | D/         | DACRATE[8:6] |           |       | PWRDN<br>ALL | DACD[3:1] 0    |              |        | 0      | 010000000 |  |

| R10(0Ah) | 0           | o           | 0           | 1           | 0           | 1           | 0      | D/         | ACRATE[8:    | 6]        | DACMS | PWRDN<br>ALL | DACD[3:1] ADCF |              |        |        | 010000000 |  |

| R11(0Bh) | 0           | 0           | 0           | 1           | 0           | 1           | 1      | ADC<br>OSR | 0            | 1         | 0     | 0            | 0              | 0            | 0      | 0      | 001000000 |  |

| R12(0Ch) | 0           | 0           | 0           | 1           | 1           | 0           | 0      | 0          | 0            | MPD       | 0     | 0            | 0              | 0            | 0      | 0      | 000000000 |  |

| R12(0Ch) | 0           | 0           | 0           | 1           | 1           | 0           | 0      | 0          | 0            | MPD       | 0     | 0            | ADCHP          | AMUTE<br>ALL | AMUTEL | AMUTER | 000000000 |  |

| R13(0Dh) | 0           | 0           | 0           | 1           | 1           | 0           | 1      | UPDATE     |              | LDA4[7:0] |       |              |                |              |        |        |           |  |

| R14(0Eh) | 0           | 0           | 0           | 1           | 1           | 1           | 0      | UPDATE     |              | RDA4[7:0] |       |              |                |              |        |        |           |  |

| R15(0Fh) | 0           | 0           | 0           | 1           | 1           | 1           | 1      | 0          | 0            | 0         | MPD   | DEEMP<br>4   | PHASE4         | DMUTE<br>4   | DZFM4  | DACD4  | 000000000 |  |

| R15(0Fh) | 0           | 0           | 0           |             |             |             | 1      | 0          | 0            | 0         | MPD   | 0            | 0              | 0            | 0      | 0      | 000000000 |  |

Device Active registers

WM8766

WM8768

WM8772

For example, active registers in the WM8768 will be shown in rows that are coloured white, light blue, and red. Similarly, registers used in the WM8772 will be in rows coloured white and green.

### **APPLICATION SUPPORT**

If you require more information or require technical support please contact Wolfson Microelectronics Applications group through the following channels:

Email: apps@wolfsonmicro.com

Telephone Apps: +44 (0)131 272 7070

Fax: +44 (0)131 272 7001

Mail: Applications at the address on last page.

or contact your local Wolfson representative.

Additional information may be made available from time to time on our web site at http://www.wolfsonmicro.com

#### **IMPORTANT NOTICE**

Wolfson Microelectronics plc (WM) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current. All products are sold subject to the WM terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

WM warrants performance of its products to the specifications applicable at the time of sale in accordance with WM's standard warranty. Testing and other quality control techniques are utilised to the extent WM deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

In order to minimise risks associated with customer applications, adequate design and operating safeguards must be used by the customer to minimise inherent or procedural hazards. Wolfson products are not authorised for use as critical components in life support devices or systems without the express written approval of an officer of the company. Life support devices or systems are devices or systems that are intended for surgical implant into the body, or support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided, can be reasonably expected to result in a significant injury to the user. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

WM assumes no liability for applications assistance or customer product design. WM does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of WM covering or relating to any combination, machine, or process in which such products or services might be or are used. WM's publication of information regarding any third party's products or services does not constitute WM's approval, license, warranty or endorsement thereof.

Reproduction of information from the WM web site or datasheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations and notices. Representation or reproduction of this information with alteration voids all warranties provided for an associated WM product or service, is an unfair and deceptive business practice, and WM is not responsible nor liable for any such use.

Resale of WM's products or services with <u>statements different from or beyond the parameters</u> stated by WM for that product or service voids all express and any implied warranties for the associated WM product or service, is an unfair and deceptive business practice, and WM is not responsible nor liable for any such use

### **ADDRESS**:

Wolfson Microelectronics plc

Westfield House

26 Westfield Road

Edinburgh

EH11 2QB

United Kingdom

Tel :: +44 (0)131 272 7000 Fax :: +44 (0)131 272 7001

Email :: sales@wolfsonmicro.com